# Unique Chips and Systems

Edited by Eugene John Juan Rubio

hhlilipad

# Unique Chips and Systems

## **Computer Engineering Series**

## Series Editor: Vojin Oklobdzija

Coding and Signal Processing for Magnetic Recording Systems Edited by Bane Vasic and Erozan M. Kurtas

> Digital Image Sequence Processing, Compression, and Analysis Edited by Todd R. Reed

Low-Power Electronics Design Edited by Christian Piguet

Unique Chips and Systems Edited by Eugene John and Juan Rubio

# Unique Chips and Systems

Edited by Eugene John Juan Rubio

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2008 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-13: 978-1-4200-5174-2 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www. copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data John, Eugene. Unique chips and systems / Eugene John and Juan Rubio. p. cm. Includes bibliographical references and index. ISBN 978-1-4200-5174-2 (hbk. : alk. paper) 1. Systems on a chip. 2. Computer networks--Equipment and supplies. I. Rubio, Juan, 1973- II. Title. TK7895.E42J64 2007 621.3815--dc22 2007024835

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

## Contents

| Pre | facevii                                                                                                                                       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Edi | torsxi                                                                                                                                        |

| Coi | ntributors xiii                                                                                                                               |

| 1   | <b>Architecture and Implementation of the TRIPS Processor</b>                                                                                 |

| 2   | <b>High-Performance Data Security in an x86 Processor</b>                                                                                     |

| 3   | <b>ARM Cortex-A8: A High-Performance Processor</b><br><b>for Low-Power Applications</b>                                                       |

| 4   | <b>A Rotated Array Clustered Extended Hypercube</b><br><b>Processor: The RACE-H<sup>TM</sup> Processor</b>                                    |

| 5   | <b>A High-Throughput Self-Timed FPGA Core Architecture</b> 125<br>Brian C. Gaide and Lizy Kurian John                                         |

| 6   | <b>The Continuation-Based Multithreading Processor: Fuce</b> 177<br>Masaaki Izumi, Satoshi Amamiya, Takanori Matsuzaki,<br>and Makoto Amamiya |

| 7   | <b>A Study of a Processor with Dual Thread Execution Modes</b> 197<br>Rania Mameesh and Manoj Franklin                                        |

| 8  | <b>Measurement-Based Power Phase Analysis</b>                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------|

| 9  | <b>Visualization by Subdivision: Two Applications</b><br><b>for Future Graphics Platforms</b>                   |

| 10 | A Performance Analysis of Two-Level Heterogeneous<br>Processing Systems on Wavefront Algorithms                 |

| 11 | <b>Microarchitectural Characteristics and Implications</b><br>of Alignment of Multiple Bioinformatics Sequences |

| 12 | <b>Towards System-Level Fault-Tolerance Using Formal</b><br><b>Methods and SoC Methodologies</b>                |

| 13 | <b>Forward Error Correction for On-Chip Interconnection</b><br><b>Networks</b>                                  |

| 14 | Alleviating Thermal Constraints while Maintaining                                                               |

| Performance via Silicon-Based On-Chip                                 |       |  |  |  |

|-----------------------------------------------------------------------|-------|--|--|--|

| Optical Interconnects                                                 | . 339 |  |  |  |

| Nicholas Nelson, Gregory Briggs, Mikhail Haurylau, Guoqing Chen,      |       |  |  |  |

| Hui Chen, Eby G. Friedman, Philippe M. Fauchet, and David H. Albonesi |       |  |  |  |

### Preface

Integrated circuits are the enabling technology for the modern information age. Advanced systems are built using state-of-the-art semiconductor chips. Computing, communication, and network chips fuel the information technology era. The demands of emerging software applications can be met only with unique chips and systems. The integration ability presented by modern semiconductor technology presents opportunities; however, the requirements posed by power consumption, reliability, and form factor present challenges. This book presents fourteen chapters dealing with several systems and chips that present unique approaches to designing future computing and communication chips and systems.

Chapter 1 presents the TRIPS processor architecture and microarchitecture. TRIPS is a unique architecture that seeks to better exploit uniprocessorlevel concurrency by changing the way instruction-level concurrency is expressed to the hardware, thereby extending the scaling of uniprocessors and enabling more efficient multiprocessors. TRIPS uses an explicit data graph execution (EDGE) instruction set architecture to efficiently encode concurrency in its dataflow execution model. The TRIPS microarchitecture uses a distributed, tiled microarchitecture that supports dynamic out-oforder execution. It is partitioned for scalability and implements deep speculation and latency tolerance.

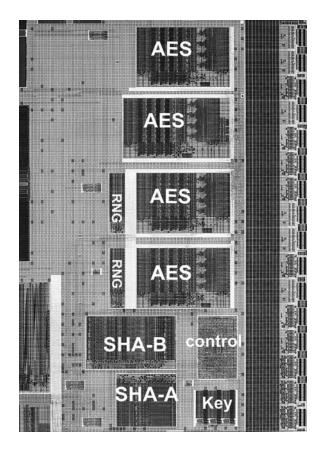

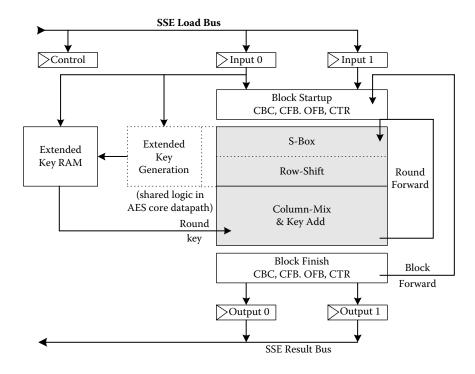

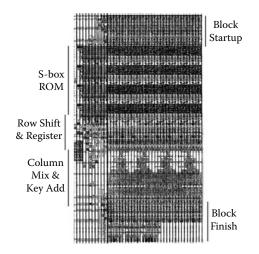

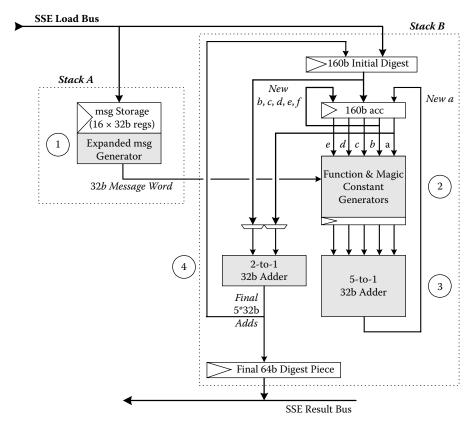

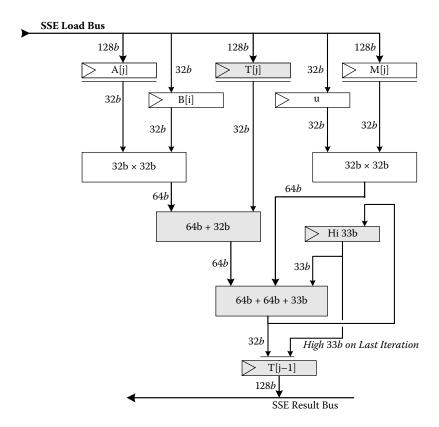

Chapter 2 describes the Centaur Technology x86 processor with several data security features. Centaur Technology (a part of VIA Technologies Inc.) integrated several security features into the x86 processor, with little increase in die size or development effort. The chapter presents the hardware security features, and describes the implementation of the AES encryption hardware, the secure hash algorithm (SHA) hardware and the Montgomery multiplier—all aimed at improving the security of the processor.

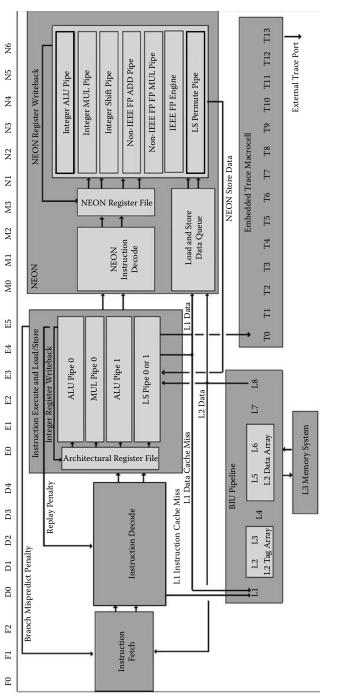

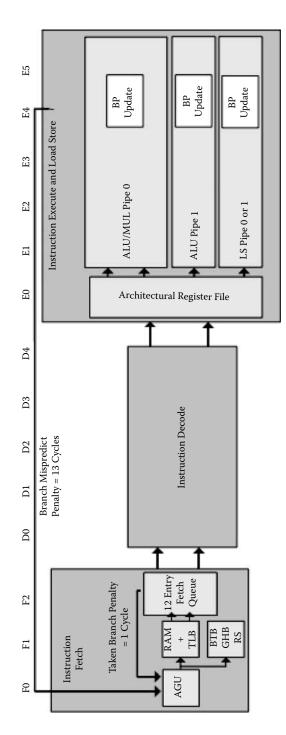

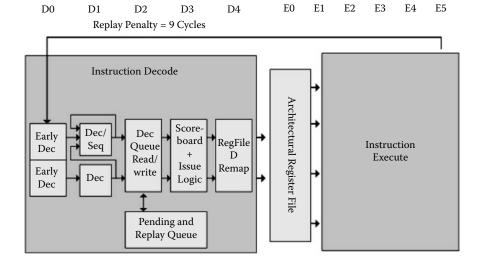

Chapter 3 presents the ARM Cortex-A8 processor, a sub-1 watt processor that provides high performance for general purpose and media applications. The processor performs superscalar execution; yet, it is designed to be energy efficient. The microarchitecture, machine efficiency, and operating frequency are decided with energy efficiency as a primary criterion. Multimedia and graphics applications are supported with a 64-bit SIMD unit.

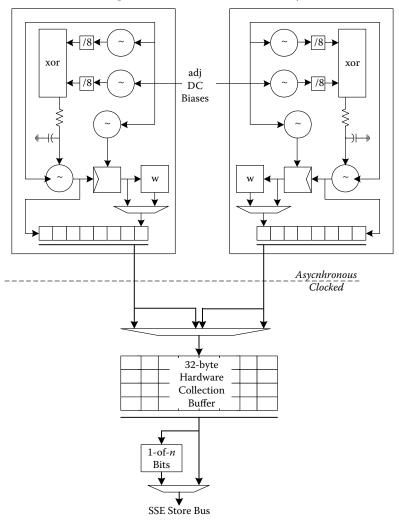

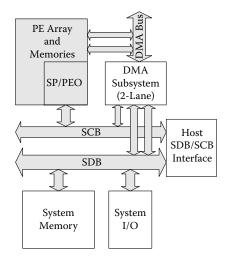

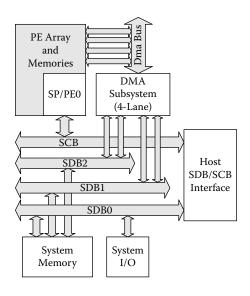

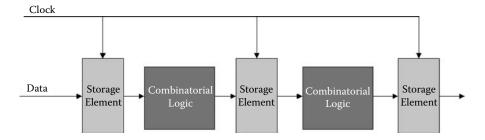

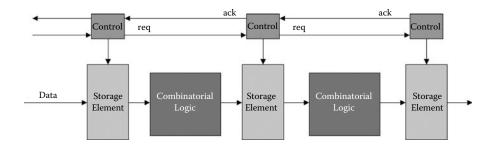

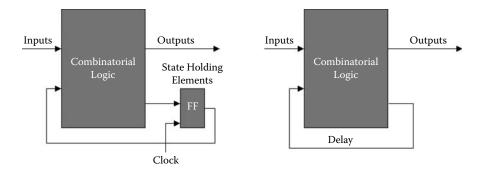

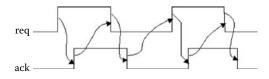

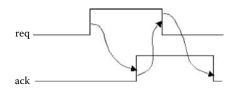

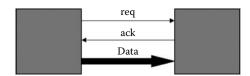

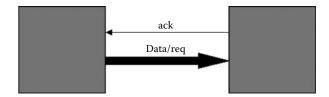

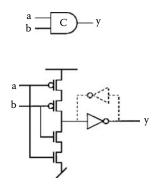

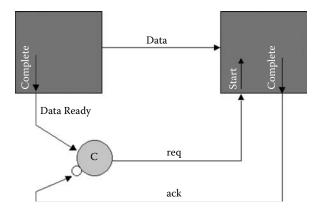

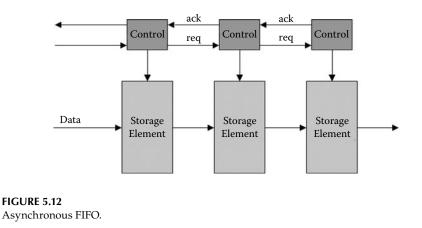

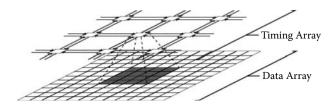

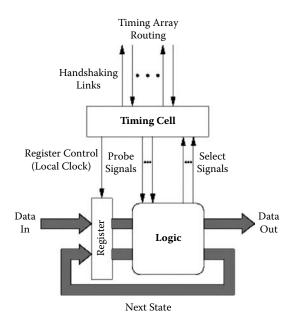

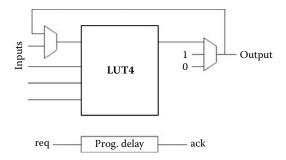

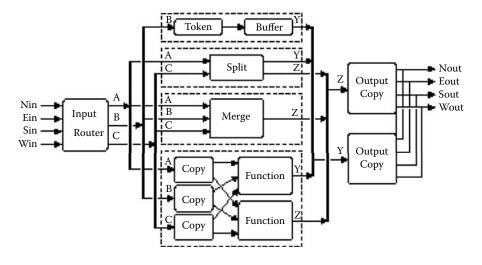

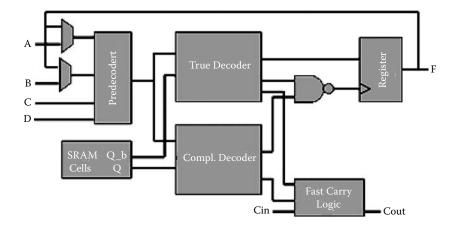

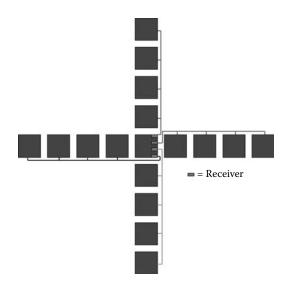

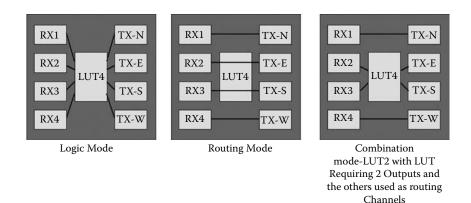

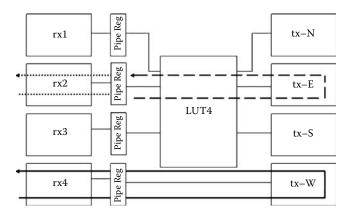

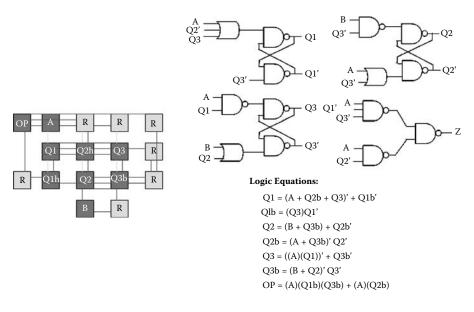

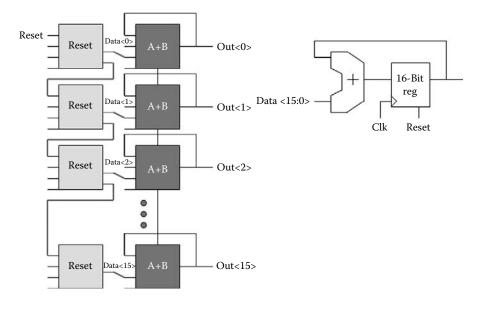

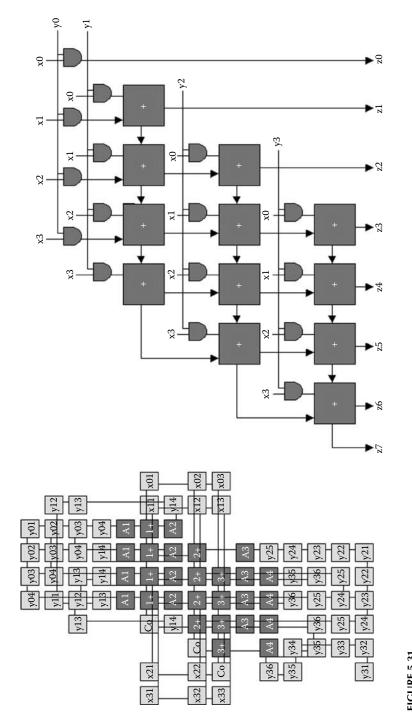

Chapter 4 presents a highly parallel signal processor, the RACE-Hypercube processor, which achieves up to 1 trillion bytes/sec at a relatively low clock frequency of 250 MHz. The processor allows the selection of a variety of configuration parameters. Chapter 5 presents an asynchronous FPGA design—the RASTER architecture. The challenges and limitation of a clocked design are overcome with a self-timed (asynchronous) design, resulting in higher performance per watt. The RASTER architecture consists of an FPGA logic cell that uses a unique method of intercell communication. Simulation shows data throughput rates of up to 1.3 GHz at the 90nm process on a benchmarking suite of small FPGA designs.

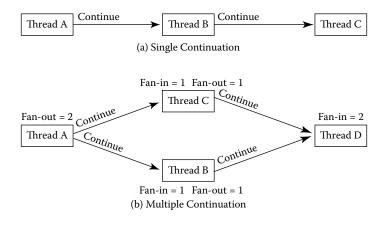

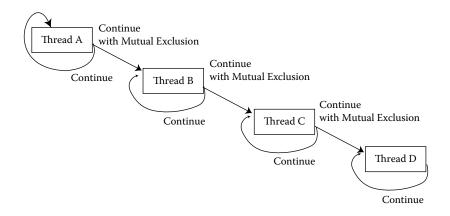

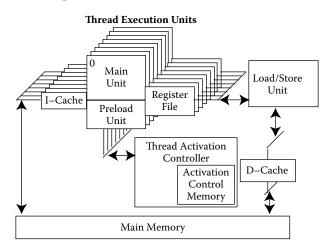

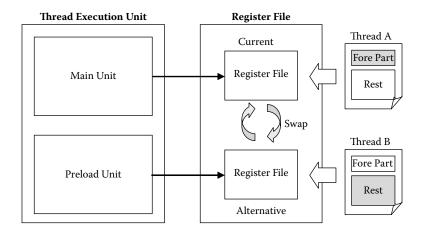

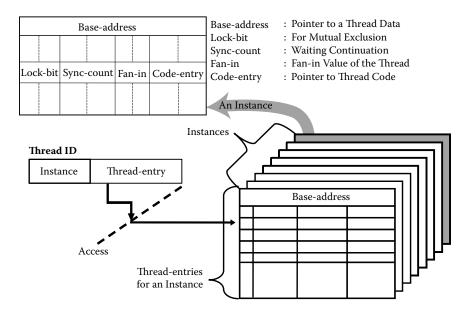

Chapter 6 presents another unique chip—the continuation-based Fuce multithreading processor. The Fuce processor from Kyushu University, Japan, is based on the dataflow computing model. The Fuce processor pursues parallel execution of threads with high parallel processing and compatibility. Fuce means "fusion of communication and execution." The Fuce processor executes multiple threads using the exclusive multithread execution model, which is derived from dataflow computing. The Fuce processor aims to fuse the interprocessor execution and interprocessor communication. The Fuce processor unifies processing inside the processor and communication with external processors using events and threads.

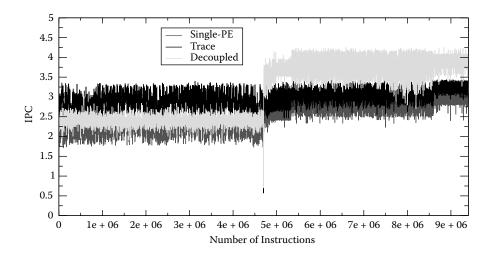

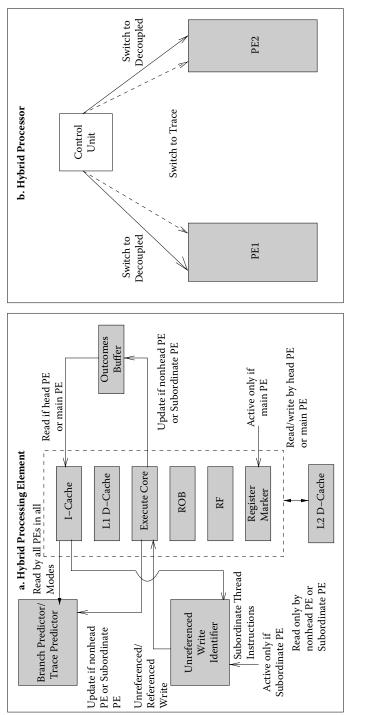

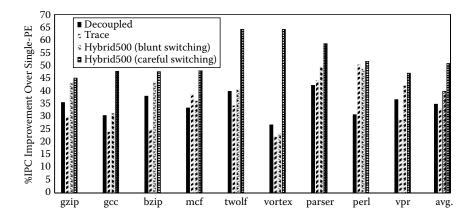

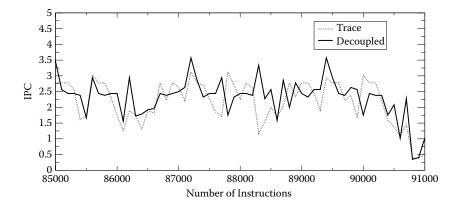

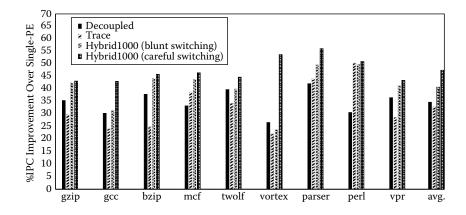

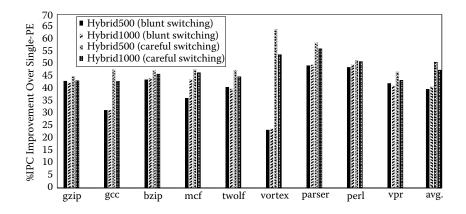

Chapter 7 is a study of a processor with dual thread execution modes. The authors present the use of additional cores on a processor for two purposes: (1) to execute subordinate threads, and (2) to execute speculative threads. Threads are spawned to the available processing cores to exploit thread-level parallelism. Performance analysis using SPEC CPU2000 benchmarks show higher improvement using subordinate threads rather than speculative threads. A processor that can switch execution modes between the two approaches is also investigated since many applications alternate between different types of phases during their execution. Such an adaptive processor is seen to be 17 percent better than the subordinate thread mechanism alone.

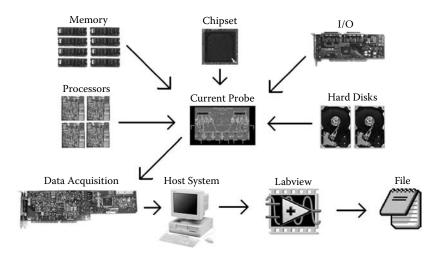

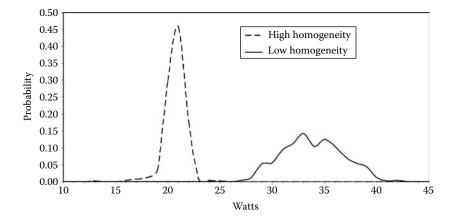

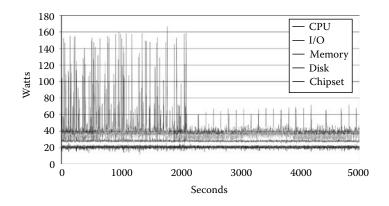

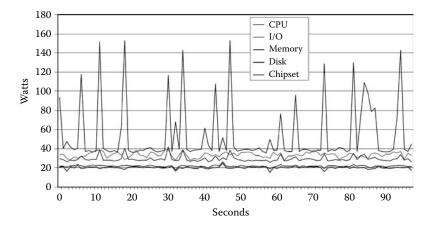

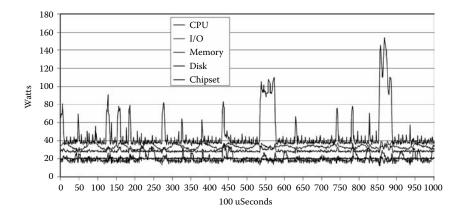

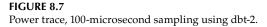

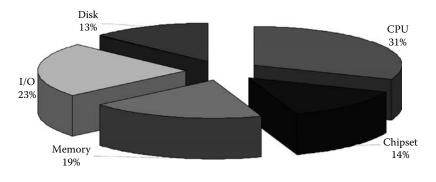

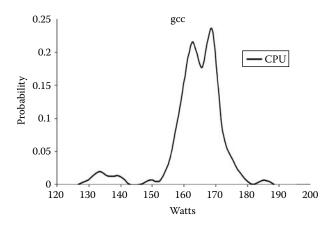

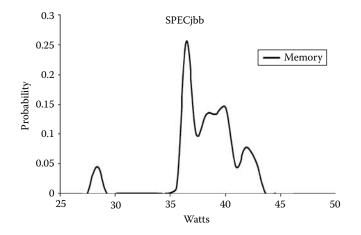

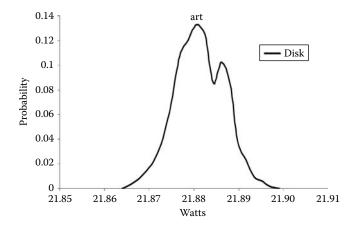

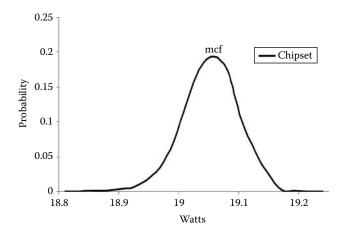

Adaptive power management of computer systems has become extremely important in recent years. Such techniques heavily rely on variation of power during execution of applications. Chapter 8 presents power phases in commercial and scientific workloads running on enterprise-class hardware. Power consumption of CPU, I/O, and disk subsystems is measured using power sensors and phase behavior of applications is studied.

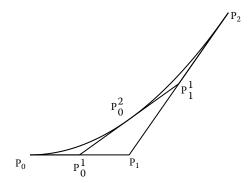

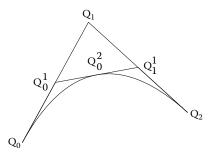

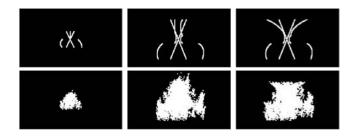

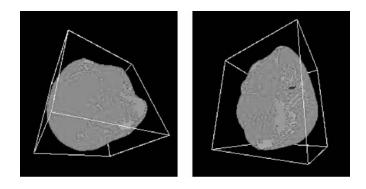

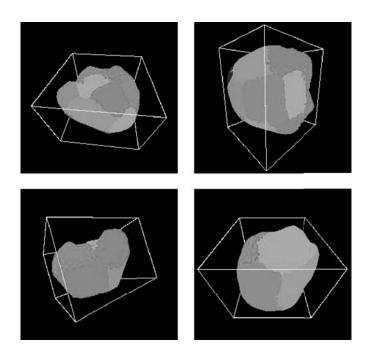

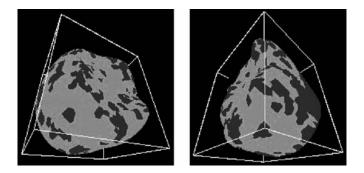

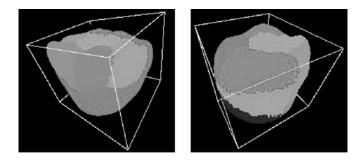

Future chips are driven by emerging and future applications. A workload that is most demanding of computational power and speed is computer graphics and visualization. Gaming has driven this quest for function and speed to such a point that graphics chips, independent of the driving computer system, have more gates than the latest CPU and many times the arithmetic power. And yet, there are aspects of graphics that still overly consume the power of systems. In Chapter 9, example graphics applications that need enormous computing power are presented. The author seeks to provide compact geometric representations of shapes so that rendering (displaying on the screen) can be more efficiently performed. He shows a close relationship between quadratic Bezier curves (QBCs) and iterated function systems (IFSs) to manipulate 2D sets that resemble 3D sets in the real world. He also

demonstrates the value of segmenting 3D triangle meshes that represent human teeth, thus dramatically accelerating visualization processes.

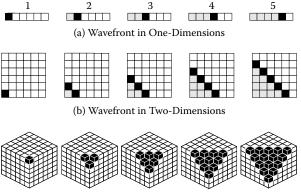

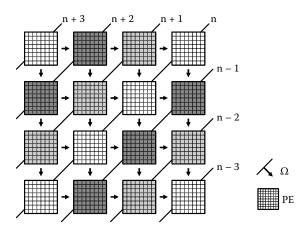

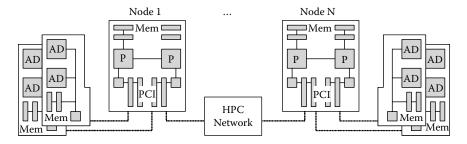

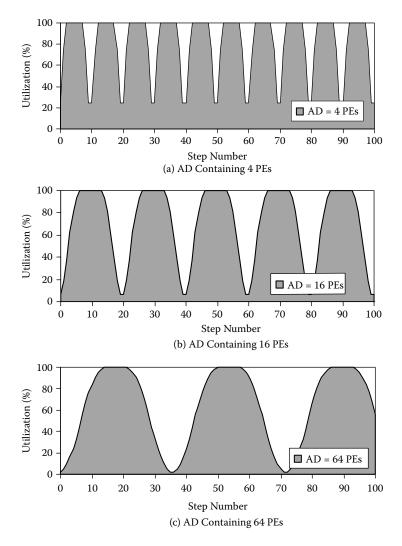

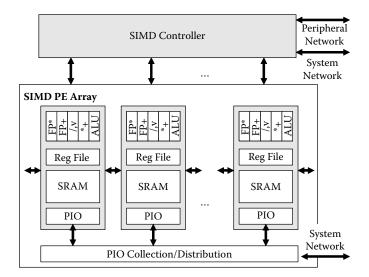

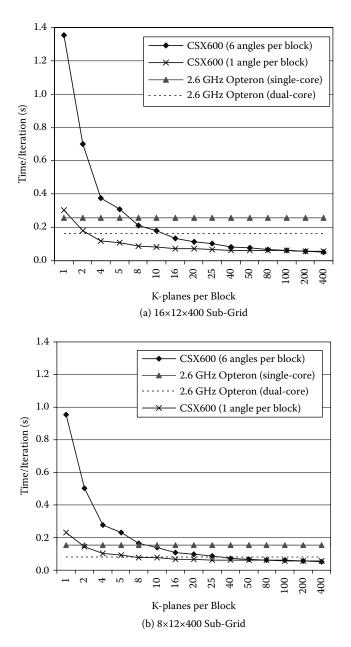

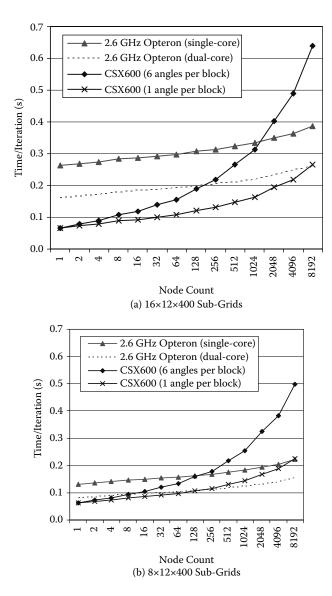

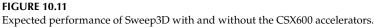

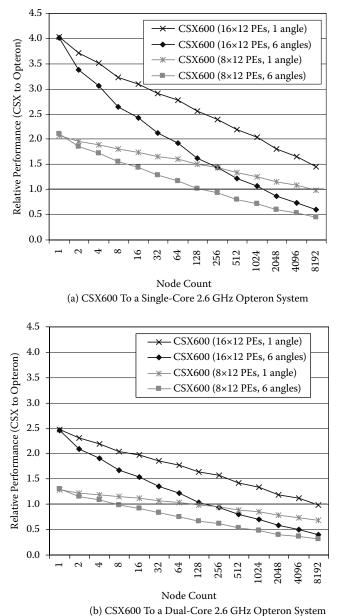

In Chapter 10, the authors illustrate the use of hardware accelerators built from field programmable gate arrays (FPGAs), graphic processing units (GPUs), or SIMD processor arrays for high performance computing. Such a system can be considered as a two-level processing system, consisting of the conventional processing nodes and the acceleration hardware connected over a high-speed network. In this chapter, researchers from the Los Alamos National Laboratory describe the use of such systems for a class of applications that use wavefront algorithms. These algorithms are characterized by a specific order in which cells are processed. The improvement in performance from accelerators such as the Clearspeed CSX600 SIMD accelerator is presented.

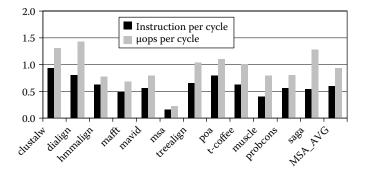

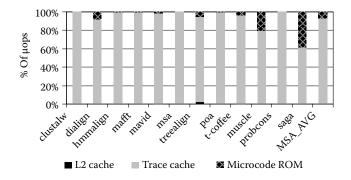

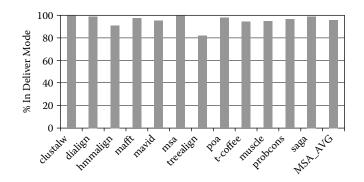

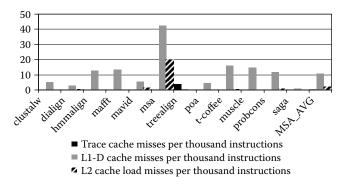

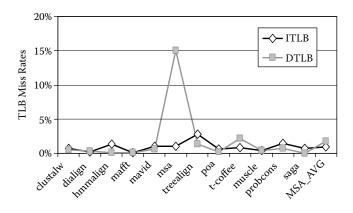

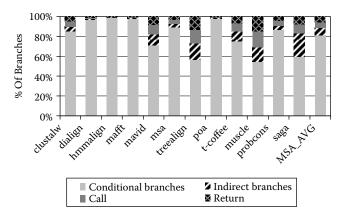

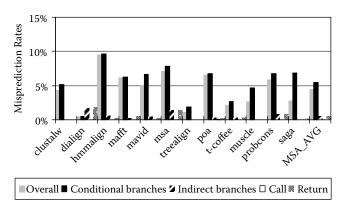

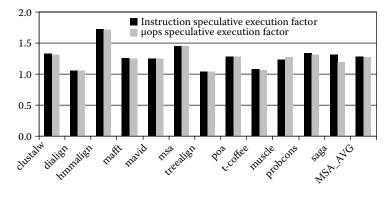

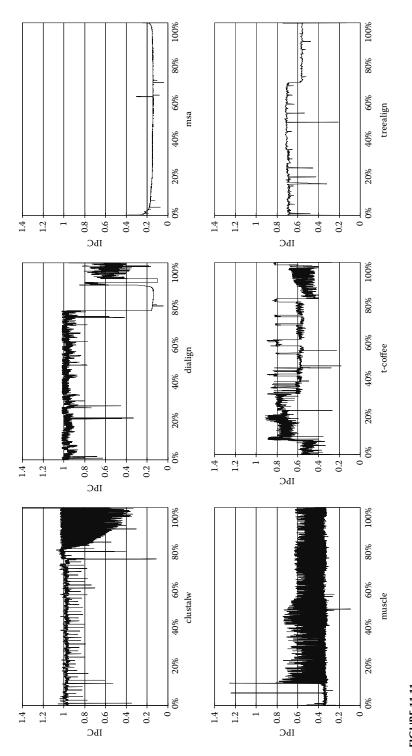

In Chapter 11, characteristics of a bioinformatics application are presented. Computational biology has become an important workload for high performance computers. Multiple-sequence alignment applications are important bioinformatics applications. Twelve multiple sequence alignment programs with a variety of alignment approaches are analyzed for performance of the cache, trace cache, branch predictor, phase behavior, and so on.

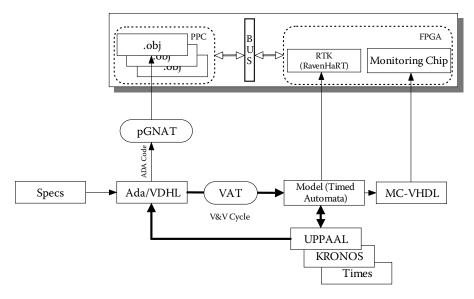

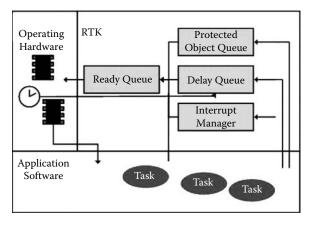

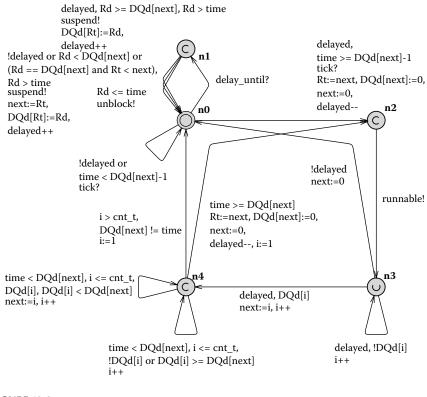

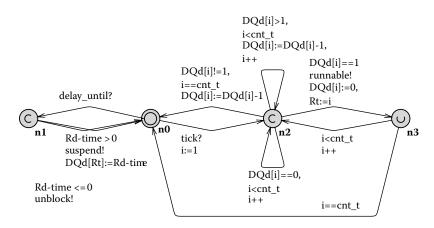

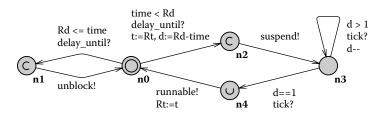

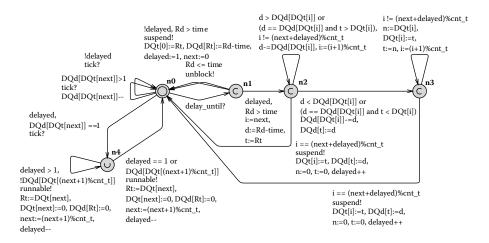

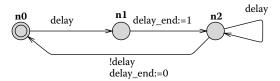

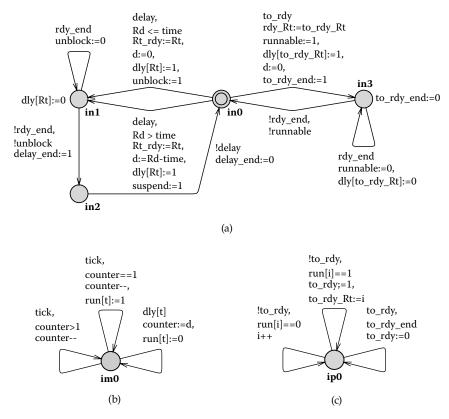

Embedded systems are inherently real time systems—they must control and compute as demanded by events. And the larger systems they are part of may demand a significant number of parallel processes going; for example, the most lavishly outfitted BMW automobile has an excess of 100 microcontrollers in charge of its many operations. Ravenscar is a subset of the Ada programming language designed for real-time computing. In Chapter 12, the authors present a Ravenscar, hardware-implemented run-time kernel with delay queues that allows for accurate analysis of application timing behavior. Formal state models and their simulations as well as hardware implementation are presented. The authors describe the corresponding VHDL state machines and demonstrate that the required levels of parallelism, hardware requirements, and timing granularity can be achieved.

In Chapter 13, an error correction scheme for a network-on-chip (NOC) is presented. The increased susceptibility of on-chip networks to various sources of error necessitates strategies to handle errors. A forward error correction scheme employing a low density parity check code (LDPC) is presented in this chapter. The presented LDPC is a linear block code suitable for low latency, high gain, and low power design because of its streamlined forward-only data flow structure.

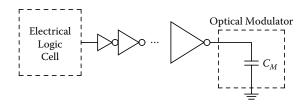

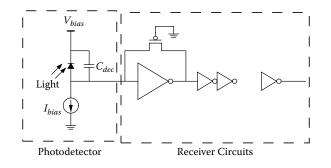

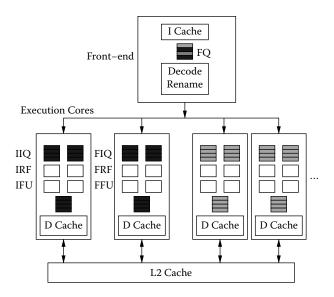

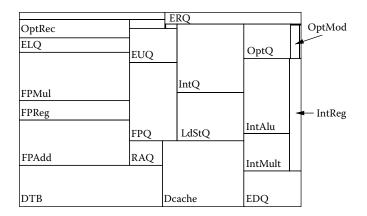

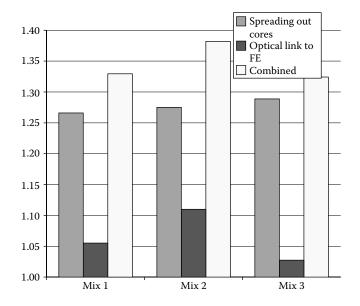

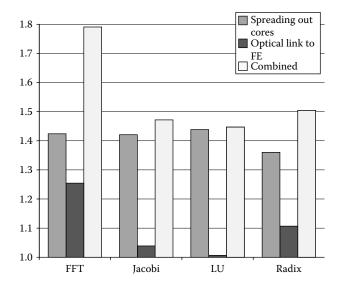

Chapter 14 presents silicon-based on-chip optical interconnects and their use in reducing thermal constraints in a high performance clustered multithreaded processor. Increased integration in modern semiconductor technologies often results in regions of the chip with very high power densities or hot spots. One technique to reduce the thermal concerns from the hot spots is to intermix hot and cold units, however, at the cost of increasing communication distances between blocks. Silicon-based optical interconnects are shown to be very valuable for global communication paths in such chips. A significant reduction in thermal constraints without reducing performance is shown in connecting the common front-end with the distributed back-end of a clustered multithreaded processor.

We hope that the readers of this book enjoy the variety of unique systems and chips presented. Most of the chapters in this book are revised versions of selected papers presented at the first, second, and third Workshop on Unique Chips and Systems (UCAS). The first and second UCAS workshops were held in March 2005 and March 2006 in Austin, Texas, and the third UCAS workshop was held in San Jose, California, in April 2007. We would like to thank the authors of the chapters for their contributions. We also wish to thank all those who helped in the process, especially Nora Konopka and Jessica Vakili at CRC Press/Francis & Taylor.

> **Eugene John** University of Texas at San Antonio

Juan Rubio IBM Austin Research Laboratory

### Editors

**Eugene John** is a professor in the department of electrical and computer engineering at the University of Texas at San Antonio. He received his Ph.D. in electrical engineering from Pennsylvania State University in 1995. His current research interests include low power circuits and systems, VLSI design, power estimation and optimization, multimedia and network processors, computer architecture, performance evaluation, and biometrics. He is a senior member of the IEEE, IEEE Computer Society, and IEEE Circuits and Systems Society. He is also a member of Eta Kappa Nu, Tau Beta Pi, and Phi Kappa Phi Honor societies.

Juan Rubio is a research staff member at the IBM Austin Research Lab. His interests include computer system architecture, performance analysis, and control systems. At IBM, he explores techniques to model, monitor and manage power; temperature and performance in computer servers; and data centers. His research contributed directly to the development of PowerExecutive<sup>TM</sup> and EnergyScale<sup>TM</sup> technology used in IBM systems.

Rubio received a B.S. in electrical engineering from Universidad Santa Maria La Antigua, Panama, in 1997, and an M.S. and Ph.D. in computer engineering from the University of Texas at Austin in 2004.

## Contributors

| David H. Albonesi Cornell University, Ithaca, New York                                                |

|-------------------------------------------------------------------------------------------------------|

| Makoto Amamiya Kyushu University, Fukuoka, Japan                                                      |

| Satoshi Amamiya Kyushu University, Fukuoka, Japan                                                     |

| <b>Frank Barry</b> Onward Communications Inc. and Appalachian State University, Boone, North Carolina |

| Praveen Bhojwani Texas A&M University, College Station, Texas                                         |

| W. Lloyd Bircher University of Texas at Austin, Texas                                                 |

| Gregory Briggs University of Rochester, Rochester, New York                                           |

| Doug Burger University of Texas at Austin, Texas                                                      |

| Guoqing Chen University of Rochester, Rochester, New York                                             |

| Hui Chen University of Rochester, Rochester, New York                                                 |

| Gwan Choi Texas A&M University, College Station, Texas                                                |

| Tom Crispin Centaur Technology Inc., Austin, Texas                                                    |

| Rajagopalan Desikan University of Texas at Austin, Texas                                              |

| Saurabh Drolia University of Texas at Austin, Texas                                                   |

| Philippe M. Fauchet University of Rochester, Rochester, New York                                      |

| Manoj Franklin University of Maryland, College Park, Maryland                                         |

| Eby G. Friedman University of Rochester, Rochester, New York                                          |

| Brian C. Gaide University of Texas at Austin, Texas                                                   |

| M. S. Govindan University of Texas at Austin, Texas                                                   |

- Paul Gratz University of Texas at Austin, Texas

- Divya Gulati University of Texas at Austin, Texas

- Heather Hanson University of Texas at Austin, Texas

- Mikhail Haurylau University of Rochester, Rochester, New York

- G. Glenn Henry Centaur Technology Inc., Austin, Texas

- Adolfy Hoisie Los Alamos National Laboratory, Los Alamos, New Mexico

- Masaaki Izumi Kyushu University, Fukuoka, Japan

- Chand T. John Stanford University, Stanford, California

- Lizy Kurian John University of Texas at Austin, Texas

- Stephen W. Keckler University of Texas at Austin, Texas

- **Darren J. Kerbyson** Los Alamos National Laboratory, Los Alamos, New Mexico

- Changkyu Kim University of Texas at Austin, Texas

- Tao Li University of Florida, Gainesville, Florida

- Haiming Liu University of Texas at Austin, Texas

- Kristina Lundqvist Massachusetts Institute of Technology, Cambridge, Massachusetts

- Rabi Mahapatra Texas A&M University, College Station, Texas

- Rania Mameesh University of Maryland, College Park, Maryland

- Takanori Matsuzaki Kyushu University, Fukuoka, Japan

- **Robert McDonald** University of Texas at Austin, Texas

- Ramadass Nagarajan University of Texas at Austin, Texas

- Nicholas Nelson University of Rochester, Rochester, New York

- Terry Parks Centaur Technology Inc., Austin, Texas

Gerald G. Pechanek Lightning Hawk Consulting Inc. Cary, North Carolina, and Priest & Goldstein, PLLC, Durham, North Carolina

Nikos Pitsianis Duke University, Durham, North Carolina

Nitya Ranganathan University of Texas at Austin, Texas

Karthikeyan Sankaralingam University of Texas at Austin, Texas

Simha Sethumadhavan University of Texas at Austin, Texas

Sadia Sharif University of Texas at Austin, Texas

Premkishore Shivakumar University of Texas at Austin, Texas

Rohit Singhal Texas A&M University, College Station, Texas

Mihailo Stojancic ViCore Technologies Inc., Palo Alto, California

David Williamson ARM Inc., Austin, Texas

## 1

## Architecture and Implementation of the TRIPS Processor

Stephen W. Keckler, Doug Burger, Karthikeyan Sankaralingam, Ramadass Nagarajan, Robert McDonald, Rajagopalan Desikan, Saurabh Drolia, M. S. Govindan, Paul Gratz, Divya Gulati, Heather Hanson, Changkyu Kim, Haiming Liu, Nitya Ranganathan, Simha Sethumadhavan, Sadia Sharif, and Premkishore Shivakumar

The University of Texas at Austin

#### CONTENTS

| 1.1 | Introduction                               |         |                                   |   |  |  |  |

|-----|--------------------------------------------|---------|-----------------------------------|---|--|--|--|

| 1.2 | ISA Support for Distributed Execution      |         |                                   |   |  |  |  |

|     | 1.2.1                                      |         | 3locks                            |   |  |  |  |

|     | 1.2.2                                      | TRIPS I | nstruction Formats                | 5 |  |  |  |

|     | 1.2.3                                      | Code G  | eneration                         | 6 |  |  |  |

| 1.3 | A Distributed Microarchitecture            |         |                                   | 8 |  |  |  |

|     | 1.3.1                                      | Global  | Control Tile (GT)                 | 9 |  |  |  |

|     |                                            | 1.3.1.1 | Fetch Unit                        |   |  |  |  |

|     |                                            | 1.3.1.2 | Refill Unit                       |   |  |  |  |

|     |                                            | 1.3.1.3 | Retire Unit                       |   |  |  |  |

|     |                                            | 1.3.1.4 | Next Block Predictor              |   |  |  |  |

|     | 1.3.2                                      | Instruc | tion Tile (IT)                    |   |  |  |  |

|     | 1.3.3                                      |         |                                   |   |  |  |  |

|     | 1.3.4                                      | Executi | on Tile (ET)                      |   |  |  |  |

|     | 1.3.5                                      | Data Ti | le (DT)                           |   |  |  |  |

|     |                                            | 1.3.5.1 | Load Processing                   |   |  |  |  |

|     |                                            | 1.3.5.2 | Store Processing                  |   |  |  |  |

|     |                                            | 1.3.5.3 | Store Tracking                    |   |  |  |  |

|     |                                            | 1.3.5.4 | Memory-Side Dependence Processing |   |  |  |  |

|     |                                            | 1.3.5.5 | Load/Store Queues                 |   |  |  |  |

|     | 1.3.6                                      | Second  | ary Memory System                 |   |  |  |  |

|     |                                            | 1.3.6.1 | OCN Router                        |   |  |  |  |

|     |                                            | 1.3.6.2 | Network Address Translation       |   |  |  |  |

| 1.4 | 4 Distributed Microarchitectural Protocols |         |                                   |   |  |  |  |

|     | 1.4.1           | Block Fetch Protocol                   | 22 |  |  |

|-----|-----------------|----------------------------------------|----|--|--|

|     | 1.4.2           | Distributed Execution                  | 24 |  |  |

|     | 1.4.3           | Block/Pipeline Flush Protocol          |    |  |  |

|     | 1.4.4           | Block Commit Protocol                  |    |  |  |

| 1.5 | Physic          | cal Design/Performance Overheads       | 27 |  |  |

|     | 1.5.1           | Chip Specifications                    | 27 |  |  |

|     | 1.5.2           | Chip Verification                      |    |  |  |

|     | 1.5.3           | TRIPS System                           | 30 |  |  |

|     | 1.5.4           | Area Overheads of Distributed Design   | 30 |  |  |

|     | 1.5.5           | Timing Overheads                       | 31 |  |  |

|     | 1.5.6           | Performance Overheads                  | 32 |  |  |

|     |                 | 1.5.6.1 Distributed Protocol Overheads | 32 |  |  |

|     |                 | 1.5.6.2 Total Performance              | 34 |  |  |

| 1.6 | Relate          | ed Work                                | 35 |  |  |

|     | 1.6.1           | Tiled Architectures                    | 35 |  |  |

|     | 1.6.2           | Dataflow Architectures                 | 36 |  |  |

|     | 1.6.3           | Superscalar Architectures              | 36 |  |  |

|     | 1.6.4           | VLIW Architectures                     |    |  |  |

| 1.7 | Concl           | usions                                 | 36 |  |  |

| Ack | Acknowledgments |                                        |    |  |  |

|     |                 | о<br>Э                                 |    |  |  |

|     |                 |                                        |    |  |  |

#### 1.1 Introduction

Growing on-chip wire delays, coupled with complexity and power limitations, have placed severe constraints on the issue-width scaling of centralized superscalar architectures. As a result, recent microprocessor designs have backed away from powerful uniprocessors, instead favoring multiple simpler cores on a single die. Partitioning the chip into a collection of processors communicating via a common memory system mitigates some of the technology scaling challenges, but increases the burden on software to provide multiple threads to execute concurrently across the cores.

An alternative is to pursue more powerful uniprocessors, but design them so that they are scalable and tolerant of technology and complexity scaling. Ideally, such wide-issue processors would be *tiled* [30], meaning composed of multiple replicated, communicating design blocks. Because of multicycle communication delays across these large processors, control must be distributed across the tiles. We advocate the use of microarchitectural networks (or *micronets*) for routing control and data among the tiles. Micronets provide high-bandwidth, flow-controlled transport for control or data in a wiredominated processor by connecting the multiple tiles, each of which is a client on one or more micronets. Higher-level microarchitectural protocols direct global control across the micronets and tiles in a manner invisible to software. In this chapter, we describe the architecture and implementation of the Teraop, Reliable, Intelligently-adaptive Processing System (TRIPS) processor—a distributed, tiled microarchitecture. In particular, we discuss TRIPS tile partitioning, micronet connectivity, and distributed protocols that provide global services in the TRIPS processor, including distributed fetch, execution, flush, and commit. Although some of our prior publications have described the TRIPS approach to exploiting parallelism as well as high-level performance results [20,3], this chapter examines in detail the intertile connectivity and protocols that have resulted from reducing the high-level design to silicon. The key concepts that differentiate TRIPS from other tiled architectures such as RAW [30] are the dynamic scheduling and execution which require distributed dynamic hardware protocols to provide the means to extract both irregular and regular concurrency.

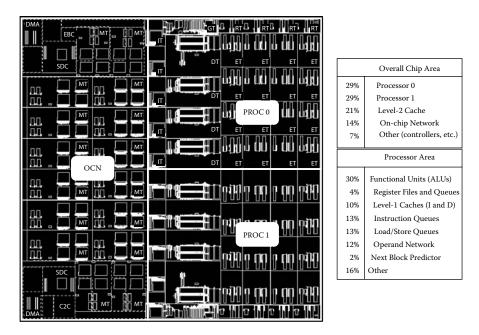

To understand the design complexity, timing, area, and performance issues of this dynamic tiled approach, we implemented the TRIPS design in a 170M transistor, 130 nm ASIC chip. This prototype chip contains two processor cores, each of which implements an EDGE instruction set architecture [3], is up to four-way multithreaded, and can execute a peak of 16 instructions per cycle. Each processor core contains five types of tiles communicating across seven micronets: one for data, one for instructions, and five for control used to orchestrate distributed execution. TRIPS prototype tiles range in size from 1–9 mm<sup>2</sup>. Four of the principal processor elements—instruction and data caches, register files, and execution units—are each subdivided into replicated copies of their respective tile type; for example, the instruction cache is composed of five instruction cache tiles.

The tiles are sized to be small enough so that wire delay within the tile is less than one cycle, and so can largely be ignored from a global perspective. Each tile interacts only with its immediate neighbors through the various micronets, which have roles such as transmitting operands between instructions, distributing instructions from the instruction cache tiles to the execution tiles, or communicating control messages from the program sequencer. By avoiding any global wires or broadcast buses—other than the clock, reset tree, and interrupt signals—this design is inherently scalable to smaller processes, and is less vulnerable to wire delays than conventional designs. Preliminary performance results on the prototype architecture using a cycle-accurate simulator show that compiled code outperforms an Alpha 21264 on half of the benchmarks, and we expect these results to improve as the TRIPS compiler and optimizations are tuned. Hand optimization of the benchmarks produces IPCs ranging from 1.5–6.5 and performance relative to Alpha of 0.6–8.

The rest of the chapter is organized as follows. Section 1.2 describes the TRIPS ISA. Section 1.3 describes the microarchitecture of the various tiles that compose the processor. This is followed by Section 1.4 which describes TRIPS microarchitectural protocols. Section 1.5 describes the physical design of the TRIPS prototype and also discusses various overheads of a distributed design. This is followed by Section 1.6, which is about related work. Finally, Section 1.7 concludes.

#### 1.2 ISA Support for Distributed Execution

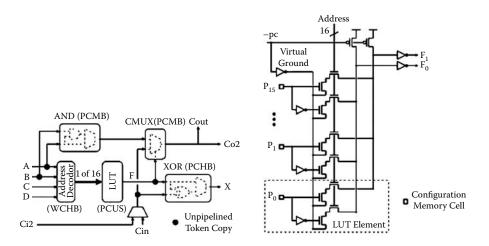

TRIPS implements an Explicit Data Graph Execution (EDGE) instruction set architecture (ISA). We conceived it with the goal of high-performance, single-threaded, concurrent but distributed execution, by allowing compilergenerated dataflow graphs to be mapped to an execution substrate by the microarchitecture. The two defining features of an EDGE ISA are (1) blockatomic execution and (2) direct communication of instructions within a block, which together enable efficient dataflow-like execution.

The TRIPS ISA aggregates up to 128 instructions into a single block that obeys the block-atomic execution model, in which a block is logically fetched, executed, and committed as a single entity. This model amortizes the perinstruction bookkeeping over a large number of instructions and reduces the number of branch predictions and register file accesses. Furthermore, this model reduces the frequency at which control decisions about what to execute must be made (such as fetch or commit), providing the additional latency tolerance to make more distributed execution practical.

#### 1.2.1 TRIPS Blocks

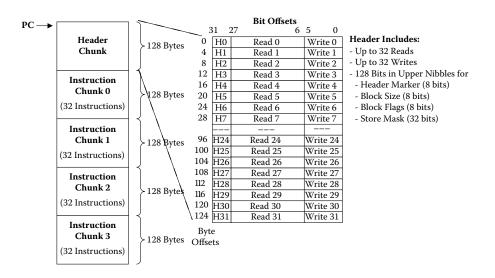

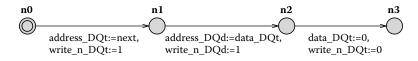

The compiler constructs TRIPS blocks and assigns each instruction to a location within the block. Each block is divided into between two and five 128byte chunks, as shown in Figure 1.1. Every block includes a header chunk that encodes up to 32 read and up to 32 write instructions that access the 128 architectural registers. The read instructions pull values out of the

FIGURE 1.1 TRIPS Block Format.

registers and send them to compute instructions in the block, whereas the write instructions return outputs from the block to the specified architectural registers. In the TRIPS microarchitecture, each of the 32 read and write instructions are distributed across the four register banks, as described in the next section.

The header chunk also holds three types of control state for the block: a 32-bit "store mask" that indicates which of the possible 32 memory instructions are stores, block execution flags that indicate the execution mode of the block, and the number of instruction "body" chunks in the block. The store mask is used, as described in Section 1.4, to enable distributed detection of block completion.

A block may contain up to four body chunks—each consisting of 32 instructions—for a maximum of 128 instructions, at most 32 of which can be loads and stores. All possible executions of a given block must emit the same number of outputs (stores, register writes, and one branch) regardless of the predicated path taken through the block. This constraint is necessary to detect block completion on the distributed substrate. The compiler generates blocks that conform to these constraints [25].

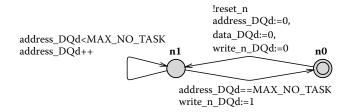

#### 1.2.2 TRIPS Instruction Formats

With *direct instruction communication*, instructions in a block send their results directly to intrablock dependent consumers in a dataflow fashion. This model supports distributed execution by eliminating the need for any intervening shared centralized structures (e.g., an issue window or register file) between intrablock producers and consumers.

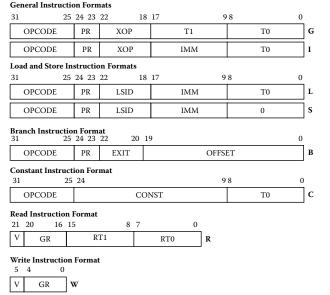

Figure 1.2 shows that the TRIPS ISA supports direct instruction communication by encoding the consumers of an instruction's result as targets within the producing instruction. The microarchitecture can thus determine precisely where the consumer resides and forward a producer's result directly to its target instruction(s). The nine-bit target fields (T0 and T1) each specify the target instruction with seven bits and the operand type (left, right, predicate) with the remaining two. A microarchitecture supporting this ISA maps each of a block's 128 instructions to particular coordinates, thereby determining the distributed flow of operands along the block's dataflow graph. An instruction's coordinates are implicitly determined by its position in its chunk, as shown in Figure 1.1.

The instruction set also includes two additional nontraditional fields: PR and LSID. The PR field is included in nearly all of the instructions and encodes a predicate to control conditional execution of the instruction. This two-bit field determines whether the instruction is unpredicated, predicated on a true condition, or predicated on a false condition. Predicated instructions must wait for a predicate operand to arrive before executing. The TRIPS predicated execution model is integrated with the datagraph execution model, enabling efficient programming and new opportunities for compiletime optimization [26]. The LSID field is five bits and is included in every

#### Instruction Fields

OPCODE = Primary Opcode XOP = Extended Opcode PR = Predicate Field IMM = Signed Immediate T0 = Target 0 Specifier T1 = Target 1 Specifier LSID = Load/Store ID EXIT = Exit Number OFFSET = Branch Offset CONST = 16-bit Constant V = Valid Bit GR = General Register Index RT0 = Read Target 0 Specifier RT1 = Read Target 1 Specifier

#### FIGURE 1.2 TRIPS Instruction Formats.

load and store instruction. This field encodes the original program order of load and store instructions within the block so that the TRIPS memory disambiguation hardware can determine when load instructions have illegally executed before store instructions on which they actually depend.

#### 1.2.3 Code Generation

The TRIPS compiler accepts sequential programs and produces explicit datagraphs for execution by the TRIPS distributed hardware resources. Front-end compilation for an EDGE instruction set is similar to that of a conventional ISA, including standard scalar optimizations. The internal representation of the code after these optimizations is similar to standard three-operand RISC code. At this stage, the EDGE blocks are merely basic blocks, and are typically quite small.

The next stage of compilation is TRIPS block formation, which uses a number of techniques to grow the block size. These optimizations include but are not limited to loop unrolling, function inlining, and if-conversion using predication. TRIPS block formation, however, is constrained by the blocksize restrictions discussed above. After block formation, a TRIPS program can be represented using our TRIPS intermediate language (TIL). This language appears similar to RISC assembly code but reflects the organization of the instructions into blocks and includes the predication and load–store identifiers. Further details on overall structure of the compiler and block formation can be found in [25, 17]. Finally, the TIL code is processed by the scheduler, which is in the back end of the compiler, to produce TRIPS assembly code (TASL). The scheduler is aware of the topology of the TRIPS core, including number of execution units and latencies between execution units. The schedule determines where each of the TRIPS instructions will execute in order to minimize the overall critical path of the block and the program. The placement of an instruction is implicitly encoded by the location of the instruction in the block chunks of Figure 1.1. Details on the algorithms employed in the scheduler can be found in [5].

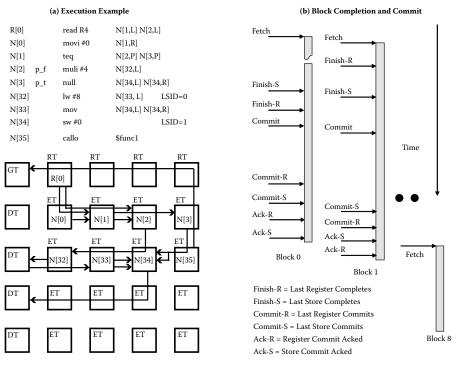

Figure 1.3 shows the transformation of a simple sequence of RISC instructions into the TRIPS TIL and TASL representations. After TRIPS block formation, the basic block of Figure 1.3a is translated into the TIL code of Figure 1.3b. The TIL code clearly delineates the block boundaries with begin and end directives. The block also shows the read and write instructions that direct values in and out of the persistent architecture register file. The TIL code further includes the predication of the branch instructions that cause execution of either block 2 or block 3 after block 1 completes. The instructions in the TIL code still appear in *operand* format in which each instruction encodes named source and destination operands.

Figure 1.3c shows the final TRIPS assembly code after block scheduling. The instructions are the same as Figure 1.3b, but each instruction has been assigned a unique identifier indicated in brackets. This unique identifier is interpreted by the hardware as the physical coordinates of a reservation

| (a) RISC basic block | (b) TRIPS TIL code | (c) TRIPS TASL code |  |  |

|----------------------|--------------------|---------------------|--|--|

|                      |                    |                     |  |  |

| ld R3,4(R2)          | .bbegin block1     | [R1] \$g1 [2]       |  |  |

| add R4,R1,R3         | read \$t1,\$g1     | [R2] \$g2 [1] [4]   |  |  |

| st R4,4(R2)          | read \$t2,\$g2     | [1] ld L[1] 4 [2]   |  |  |

| addi R5,R4,#2        | ld \$t3,4(\$t2)    | [2] add [3] [4]     |  |  |

| beqz R4,Block3       | add \$t4,\$t1,\$t3 | [3] mov [5] [6]     |  |  |

|                      | st \$t4,4(\$t2)    | [4] st S[2] 4       |  |  |

|                      | addi \$t5,\$t4,2   | [5] addi 2 [W1]     |  |  |

|                      | teqz \$t6,\$t4     | [6] teqz [7] [8]    |  |  |

|                      | b_t<\$t6> block3   | [7] b_t block3      |  |  |

|                      | b_f<\$t6> block2   | [8] b_f block2      |  |  |

|                      | write \$g5,\$t5    | [W1] \$g5           |  |  |

|                      | .bend block1       |                     |  |  |

|                      |                    |                     |  |  |

|                      | .bbegin block2     |                     |  |  |

|                      |                    |                     |  |  |

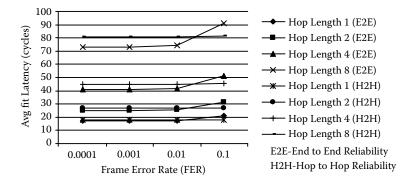

**FIGURE 1.3** Transformation of RISC code to TRIPS assembly code.

station. The instructions are now in *target* format in which each instruction specifies the identifiers of the consumers of its result, but instructions do not encode from where their operands are coming. The load and store instructions now include the load–store sequence numbers (LSID) and the instruction stream includes a new mov instruction. This mov serves to fan out the result of the previous add instruction to a total of three targets. The add cannot complete this task itself because instruction encodings are limited to two targets for arithmetic instructions.

#### 1.3 A Distributed Microarchitecture

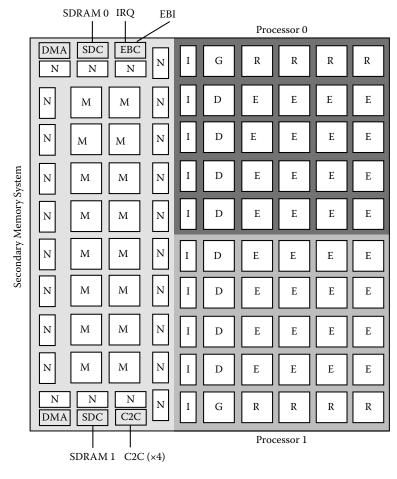

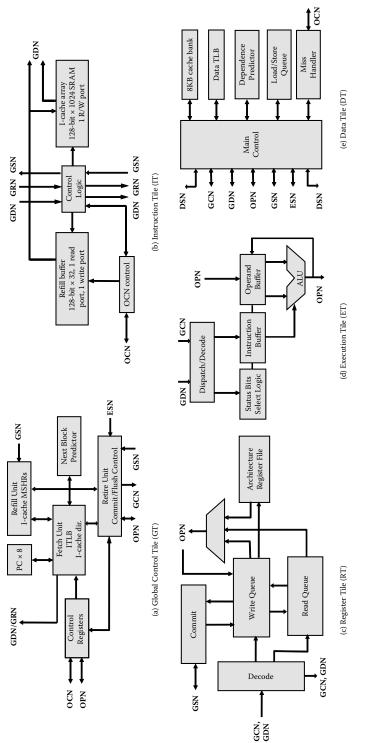

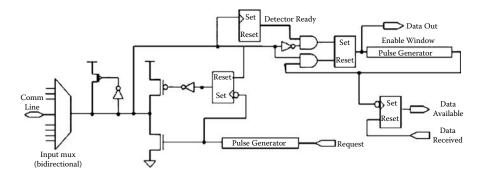

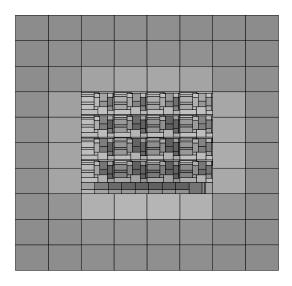

The goal of the TRIPS microarchitecture is a processor that is scalable and distributed, meaning that it has no global wires, is built from a small set of reused components on routed networks, and can be extended to a widerissue implementation without recompiling source code or changing the ISA. Figure 1.4 shows the tile-level block diagram of the TRIPS prototype that meets these specifications. The three major components on the chip are two processors and the secondary memory system, each connected internally by one or more micronetworks.

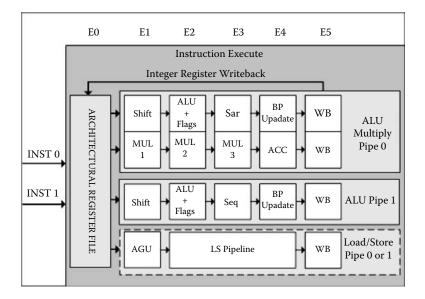

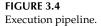

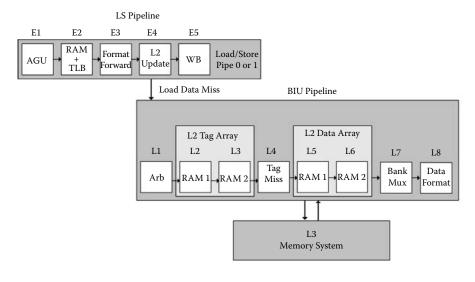

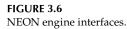

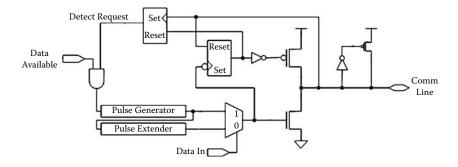

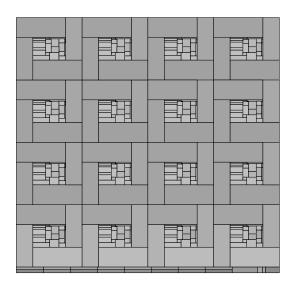

Each of the processor cores is implemented using five unique tiles: one global control tile (GT), 16 execution tiles (ET), four register tiles (RT), four data tiles (DT), and five instruction tiles (IT). The main processor core micronetwork is the operand network (OPN), shown in Figure 1.5. It connects all of the tiles except for the ITs in a two-dimensional, wormhole-routed,  $5 \times 5$  mesh topology. The OPN has separate control and data channels, and can deliver one 64-bit data operand per link per cycle. A control header packet is launched one cycle in advance of the data payload packet to accelerate wakeup and select for bypassed operands that traverse the network.

Each processor core contains six other micronetworks, one for instruction dispatch—the global dispatch network (GDN)–and five for control: global control network (GCN), for committing and flushing blocks; global status network (GSN), for transmitting information about block completion; global refill network (GRN), for I-cache miss refills; data status network (DSN), for communicating store completion information; and external store network (ESN), for determining store completion in the L2 cache or memory. Links in each of these networks connect only nearest neighbor tiles and messages traverse one tile per cycle. Figure 1.5 shows the links for three of these networks.

This type of tiled microarchitecture is *composable* at design time, permitting different numbers and topologies of tiles in new implementations with only moderate changes to the tile logic, and no changes to the software model. The particular arrangement of tiles in the prototype produces a core with 16-wide out-of-order issue, 80 KB of L1 instruction cache, 32 KB of L1 data cache, and four SMT threads. The microarchitecture supports up to eight TRIPS blocks in flight simultaneously, seven of them speculative if a single thread

FIGURE 1.4

is running, or two blocks per thread if four threads are running. The eight 128-instruction blocks provide an in-flight window of 1,024 instructions.

The two processors can communicate through the secondary memory system, in which the On-Chip Network (OCN) is embedded. The OCN is a  $4 \times 10$ , wormhole-routed mesh network, with 16-byte data links and four virtual channels. This network is optimized for cache-line sized transfers, although other request sizes are supported for operations such as loads and stores to uncacheable pages. The OCN acts as the transport fabric for all interprocessor, L2 cache, DRAM, I/O, and DMA traffic.

#### 1.3.1 Global Control Tile (GT)

Figure 1.6a shows the contents of the GT, which include the blocks' PCs, the instruction cache tag arrays, the I-TLB, and the next-block predictor. The GT

FIGURE 1.5 TRIPS micronetworks.

handles TRIPS block management, including prediction, fetch, dispatch, completion detection, flush (on mispredictions and interrupts), and commit. It also holds control registers that configure the processor into different speculation, execution, and threading modes. Thus the GT interacts with all of the control networks and the OPN, to provide access to the block PCs. The GT also maintains the current status of all eight in-flight blocks. When one of the block slots is free, the GT accesses the block predictor, which takes three cycles, and emits the predicted address of the next target block. Each block may emit only one "exit" branch, even though it may contain several predicated branches.

#### 1.3.1.1 Fetch Unit

The fetch unit consists of a TLB (Translation-Lookaside Buffer) and a directory of the blocks that are resident in the I-cache. In addition, it contains the

program counters (PC) for each thread and control registers that are used to configure the execution of each block.

The instructions of a TRIPS block are striped across all of the ITs. For example, IT0 caches chunk 0 of a block and IT1 caches chunk 1 of the same block. The I-cache directory contains a listing of all blocks that are currently resident in the I-cache. The directory consists of 128 entries, organized in a two-way set-associative fashion, and each entry identifies a unique cached block. The directory is virtually indexed and entries are evicted and replaced in a LRU fashion.

The I-cache directory is similar to the tag array in conventional caches. In the TRIPS processor, the GT maintains a single array on behalf of all the ITs. This centralized directory provides a consistent view of the cached blocks and avoids scenarios where portions of a block are not present in the I-cache. The tag array in each IT can be eliminated, thus simplifying the implementation in both the GT and ITs. An alternate design could maintain the tag array as part of each IT. However, since a single block is striped across all ITs and each of them operates because in a distributed fashion, this approach would require special hardware to keep the tag arrays consistent.

The instruction TLB (ITLB) consists of a set of sixteen registers to provide the translations of virtual addresses of blocks to physical addresses. Each register defines the size and read/execute access attributes of up to sixteen memory segments. The minimum size of a memory segment is 64 KB and the maximum size is 1 TB. Instruction memory segments may be marked as uncacheable in the L1. A block in such a segment will never be filled into the I-cache. A miss in the ITLB or an access protection violation will generate an exception. Similar to the I-cache directory, implementing the ITLB inside the GT avoids redundant implementation in the ITs.

#### 1.3.1.2 Refill Unit

The refill unit maintains the status of pending I-cache refills. The TRIPS processor supports up to four outstanding refills, but at most one per thread. To manage multiple outstanding refills, the GT tracks the I-cache set and the way being refilled and whether the refill has completed. The storage for tracking pending refills in the GT is similar to the I-cache MSHR (Miss Status Handling Register) state in conventional processors.

#### 1.3.1.3 Retire Unit

The retire unit contains a retirement table, which tracks the execution state of all blocks in flight, and is responsible for initiating the flush, commit, and deallocation of the blocks in flight. Table 1.1 shows the details of the state maintained for each block. Some of the entries in this table are locally initialized by the GT, when it starts various block-level operations. Other state, which manages the completion and commit protocols, is updated as blocks produce their register, memory, and branch outputs. Neighboring

| TADLE 1.1                                            |                              |  |  |  |  |

|------------------------------------------------------|------------------------------|--|--|--|--|

| State Tracked for Each Block in the Retirement Table |                              |  |  |  |  |

| V                                                    | Valid block                  |  |  |  |  |

| 0                                                    | Oldest block in thread       |  |  |  |  |

| Y                                                    | Youngest block in thread     |  |  |  |  |

| BADDR                                                | Virtual address of the block |  |  |  |  |

| PADDR Predicted address of the next block            |                              |  |  |  |  |

| RADDR Actual resolved address of the next bl         |                              |  |  |  |  |

| RC                                                   | Registers completed          |  |  |  |  |

| SC                                                   | Stores completed             |  |  |  |  |

| BC                                                   | Branch completed             |  |  |  |  |

| RCOMM                                                | Registers committed          |  |  |  |  |

| SCOMM                                                | Stores committed             |  |  |  |  |

| Е                                                    | Exception in block           |  |  |  |  |

| F                                                    | Block already flushed        |  |  |  |  |

#### TABLE 1.1

tiles deliver updates to this state to the GT using the TRIPS processor control networks.

The retirement table is similar to the reorder buffer (ROB) in conventional processors. However, this table does not track the status of individual instructions. It has only one entry for each block, thus containing far fewer entries than a conventional ROB.

#### 1.3.1.4 Next Block Predictor

The next block predictor uses a branch instruction's three-bit exit field to construct exit histories instead of using taken/not-taken bits. The predictor has two major parts: an exit predictor and a target predictor. The predictor uses exit histories to predict one of eight possible block exits, employing a tournament local/gshare predictor similar to the Alpha 21264 [13] with 9 K, 16 K, and 12 K bits in the local, global, and choice exit predictors, respectively. The predicted exit number is combined with the current block address to access the target predictor for the next-block address. The target predictor contains four major structures: a branch target buffer (20 K bits), a call target buffer (6 K bits), a return address stack (7 K bits), and a branch type predictor (12 K bits). The BTB predicts targets for branches, the CTB for calls, and the RAS for returns. The branch type predictor selects among the different target predictions (call/return/branch/sequential branch). The distributed fetch protocol necessitates the type predictor; the predictor never sees the actual branch instructions, as they are sent directly from the ITs to the ETs.

The predictor performs three major operations: *predict, update,* and *repair*. Predict provides a prediction for the next block. Update modifies the predictor

tables with the information from a committing block. Repair corrects any predictor state modified by incorrect speculation. Each of the three operations consumes three processor cycles.

#### **1.3.2** Instruction Tile (IT)

Figure 1.6b shows an IT containing a two-way, 16 KB bank of the total L1 Icache. The ITs act as slaves to the GT, which holds the single tag array. Each of the five 16 KB IT banks can hold a 128-byte chunk (for a total of 640 bytes for a maximum-sized block) for each of 128 distinct blocks. An instruction cache tile also contains a 32-entry refill buffer with 128-bit entries. On an instruction cache miss, each IT will independently fetch its portion of the missed block into its own refill buffer. Later, when the block is dispatched, the contents of the refill buffer are delivered into the execution unit array and written into the instruction cache RAM. The refill buffer has room for four fetched blocks that are waiting to be dispatched.

#### 1.3.3 Register Tile (RT)

To reduce power consumption and delay, the TRIPS microarchitecture partitions its many registers into banks, with one bank in each RT. The register tiles are clients on the OPN, allowing the compiler to place critical instructions that read and write from/to a given bank close to that bank. Because many def-use pairs of instructions are converted to intrablock temporaries by the compiler, they never access the register file, thus reducing total register bandwidth requirements by approximately 70%, on average, compared to a RISC or CISC processor. The four distributed banks can thus provide sufficient register bandwidth with a small number of ports; in the TRIPS prototype, each RT bank has two read ports and one write port. Each of the four RTs contains one 32-register bank for each of the four SMT threads that the core supports, for a total of 128 registers per RT and 128 registers per thread across the RTs.

In addition to the four per-thread architecture register file banks, each RT contains a read queue and a write queue, as shown in Figure 1.6c. These queues hold up to eight read and eight write instructions from the block header for each of the eight blocks in flight, and are used to forward register writes dynamically to subsequent blocks reading from those registers. The read and write queues perform a function equivalent to register renaming for a superscalar physical register file, but are less complex to implement due to the read and write instructions in the TRIPS ISA.

When a block dispatches, the read and write instructions are delivered to the RTs where they are captured in the read and write queues, respectively. Each read instruction queries the write queue, searching for write instructions from prior uncommitted blocks. If the read instruction finds that the most recent write queue entry to the sought after register has a valid value, it injects the value into the execution array. On the other hand, if it finds that the most recent write instruction does not yet have a valid value, it stays in the read queue. When the prior block produces the register write, the pending register read wakes up and forwards the written value to its descendants. If the read instruction finds no matching write instruction in the write queue, it reads from the persistent register file. Register reads and forwarding of writes from prior blocks may be speculative and occur before the previous block commits. Speculation recovery involves invalidating the read and write queue entries of all affected blocks.

#### 1.3.4 Execution Tile (ET)

As shown in Figure 1.6d, each of the 16 ETs consists of a fairly standard single-issue pipeline, a bank of 64 reservation stations, an integer unit, and a floating-point unit. All units are fully pipelined except for the integer divide unit, which takes 24 cycles. The 64 reservation stations hold eight instructions for each of the eight in-flight TRIPS blocks. Each reservation station has fields for two 64-bit data operands and a one-bit predicate. Arriving operands specify the exact reservation station to write into, eliminating the need for a CAM structure in the reservation stations; the TRIPS microarchitecture uses a lower power RAM structure instead.

Each ET is responsible for local wakeup and selection of instructions. According to the dataflow execution model, any instruction that has all of its operands present may be selected for execution. If more than one instruction is ready, the ET selects the oldest instruction, which corresponds to the earliest fetched instruction from the oldest block. When in the multithreaded configuration, the ET may be selecting instructions from up to four threads. In this case, selection priority rotates among the four threads, and within each thread the oldest instruction is given the highest priority.

When an instruction completes, the ET is responsible for forwarding the result to the target instructions. If the target resides on the same ET, the result can bypass directly to the target instruction for immediate execution; no bubbles between dependent instructions are required. If the target is remote, the ET injects the result into the operand network for delivery. If the instruction has multiple targets, the ET injects a separate message into the network for each target on successive cycles. When an operand arrives from a remote ET, the control packet arrives first and begins the wakeup process. If the ET selects the instruction receiving the operand, the instruction may rendezvous with the operand network data packet arriving on the next cycle and execute immediately. At a minimum, only one pipeline bubble is required between dependent instructions executing on adjacent ETs.

The ETs also implement the TRIPS predication and exception models. Unlike other predicated architectures, TRIPS only executes a predicated instruction if the arriving predicate polarity (true or false) matches the polarity of the predicated instruction. The ET matches arriving predicates to predicated instructions and keeps unmatched predicated instructions in their reservation stations until a matching predicate arrives. In TRIPS, an instruction that causes an exception cannot immediately signal the problem because the instruction may be speculative. Instead, the ET generates a poison bit that propagates with the instruction through the datagraph execution. The processor will detect an exception only if the poison bit propagates to a block output (register write, store, or branch target) and the block is ready to commit. On a block flush or commit, the ET removes all of the flushed block's pending instructions from the reservation stations and any of the block's operand packets still propagating through the operand network.

#### 1.3.5 Data Tile (DT)

Figure 1.6e shows a block diagram of a single DT. Each DT is a client on the OPN, and holds one 2-way, 8 KB L1 data cache bank, for a total of 32 KB across the four DTs. Virtual addresses are interleaved across the DTs at the granularity of a 64-byte cache-line. In addition to the L1 cache bank, each DT contains a copy of the load/store queue (LSQ), a dependence predictor, a one-entry back-side coalescing write buffer, a data TLB, and a MSHR that supports up to 16 requests for up to four outstanding cache lines.

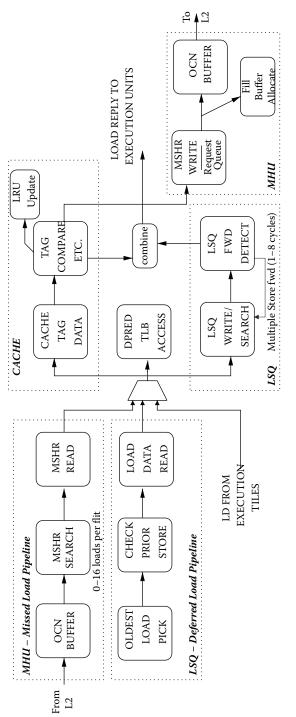

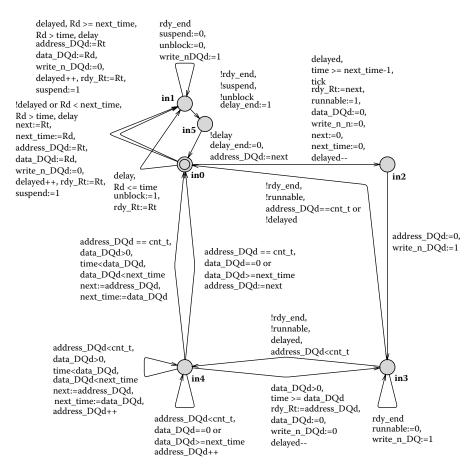

#### 1.3.5.1 Load Processing

The pipeline diagram in Figure 1.7 illustrates the different stages of load processing. Every incoming load accesses (a) the TLB to perform address translation and check the protection attributes, (b) the dependence predictor (DPR) to check for possible store dependences, (c) the LSQ to identify older matching uncommitted stores, and (d) the cache tags to check for cache hits. Based on the responses (hit/miss) from the four units, the control logic decides on the course of action for that load. Table 1.2 summarizes the possible load execution scenarios in the DT.

When the load hits in the cache, and only in the cache, the load reply can be generated in two cycles. This best-case latency is likely to be the common case for most loads. When a load hits both in the cache and the LSQ, the load return value is formed by composing the values obtained from the LSQ and cache. First, the load picks up any matching store's bytes from the LSQ and then reads the remaining bytes from the cache. This operation can take multiple cycles and is referred to as store forwarding.

A load may arrive at the DT before an earlier store on which it depends. Processing such a load right away will result in a dependence violation and a flush, leading to performance losses. To avoid this performance loss, the TRIPS processor employs a simple dependence predictor that predicts whether the load processing should be deferred. If the DPR predicts a likely dependence, the load waits in the LSQ until all prior stores have arrived. After the arrival of all older stores, the load is enabled from the LSQ, and allowed to access the cache and the LSQs to obtain the most recent updated store value.

FIGURE 1.7 The DT load pipelines.

| TLB  | DPR  | Cache | LSQ  | Response                                             |

|------|------|-------|------|------------------------------------------------------|

| Miss | Х    | Х     | х    | Report TLB Exception                                 |

| Hit  | Hit  | Х     | Х    | Defer load until all prior stores are received       |

| Hit  | Miss | Hit   | Miss | Forward data from cache                              |

| Hit  | Miss | Miss  | Х    | Forward data from L2 cache, issue cache fill request |

| Hit  | Miss | Hit   | Hit  | Forward data from LSQ and cache                      |

## TABLE 1.2 Load Execution Scenarios

Note: X represents "don't care" state.

If the load misses in the cache, it is buffered in the MSHRs [16] and a read request is generated and sent to the L2. When the data is returned from the L2, the loads in the MSHRs are enabled and load processing resumes. As with deferred loads, missed loads also access the LSQ and cache to pick up the most recent store values.

#### 1.3.5.2 Store Processing

Store processing occurs in two phases. During the first phase, each incoming store is buffered in the LSQ and the other DTs are notified about the store's arrival using the Data Status Network (DSN). During this phase each store checks for dependence violations; if any younger loads to the same address as the store are in the queue, then a violation is reported to the control unit, which initiates recovery. The dependence predictor is also trained to prevent such violations in the future.

When a block becomes nonspeculative, the second phase of store processing begins as illustrated in Figure 1.8. In this phase the oldest store is removed from the LSQ, checked in the TLB, and the store value is written out to the cache/memory system. If the store hits in the cache, the corresponding cache line is marked as dirty. If the store misses in the cache, the store miss request is sent to the L2. We chose a write-back, write-no allocate policy to minimize the number of commit stalls.

|                 | Cycle 1                 | Cycle 2                        | Cycle 3                 | Cycle 4                                | Cycle 5                                 |

|-----------------|-------------------------|--------------------------------|-------------------------|----------------------------------------|-----------------------------------------|

| Store<br>Commit | Pick Store<br>to Commit | Read<br>Store Data<br>from LSQ | Access<br>Cache<br>Tags | Check for<br>Hit or Miss<br>LRU Update | Write to<br>Cache or<br>Merge<br>Buffer |

**FIGURE 1.8** Store commit pipeline.

#### 1.3.5.3 Store Tracking

In the TRIPS execution model, a block can commit only after all of its store outputs have been generated. When a store arrives at any DT, the store arrival information is broadcast to the other DTs through the DSN. Each DT then increments a local counter that counts the number of stores that have arrived at the memory system. When all of the stores in a block have been received, the DT that received the last store sends a message to the control tile indicating that all memory outputs have been generated.

#### 1.3.5.4 Memory-Side Dependence Processing

Because the DTs are distributed in the network, we implemented a memoryside dependence predictor, closely coupled with each data cache bank [23]. Although loads issue from the ETs, a dependence prediction occurs (in parallel) with the cache access only when the load arrives at the DT. A naive extension of conventional dependence processing mechanisms [4] would hold back the load in the execution unit until the execution of the dependent store.

In TRIPS, the latency of dependent loads can be broken down into four parts: (1) the latency for the load to detect that the dependent store has executed, (2) the latency for the load to be delivered from the execution unit to the DT, (3) the latency to access the DT, and (4) the latency to deliver the value from the DT to the target of the load. With execution-side dependence processing, the system cannot overlap any of the latencies, because the loads are issued only after the dependent stores resolve and rest of the steps must be performed in order. However, memory-side dependence processing allows the overlap of steps (1) and (2).

The dependence predictor in each DT uses a 1024-entry bit vector. When an aggressively issued load causes a dependence misprediction (and subsequent pipeline flush), the dependence predictor sets a bit to which the load address hashes. Any load whose predictor entry contains a set bit is stalled until all prior stores have completed. Because there is no way to clear individual bit vector entries in this scheme, the hardware clears the dependence predictor after every 10,000 blocks of execution.

#### 1.3.5.5 Load/Store Queues

The hardest challenge in designing a distributed data cache is the memory disambiguation hardware. Because the TRIPS ISA restricts each block to 32 maximum issued loads and stores and eight blocks can be in flight at once, up to 256 memory operations may be in flight. However, the mapping of memory operations to DTs is unknown until their effective addresses are computed. Two resultant problems are: (a) determining how to distribute the LSQ among the DTs, and (b) determining when all earlier stores have completed—across all DTs—so that a held-back load can issue.

Although neither centralizing the LSQ nor distributing the LSQ capacity across the four DTs were feasible options at the time, we solved the LSQ distribution problem largely by brute force. We replicated four copies of a 256-entry LSQ, one at each DT. This solution is wasteful and not scalable (because the maximum occupancy of all LSQs is 25%), but was the least complex alternative for the prototype. The LSQ can accept one load or store per cycle, forwarding data from earlier stores as necessary. Additional details on the DT and LSQ design can be found in [23].

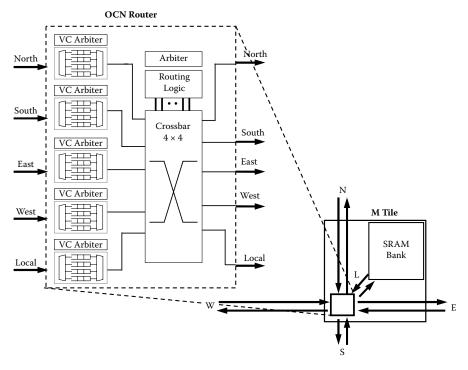

#### 1.3.6 Secondary Memory System

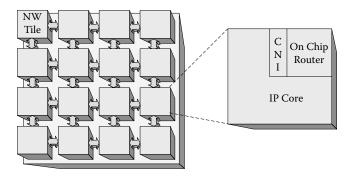

The TRIPS prototype supports a 1 MB static NUCA [14] array, organized into 16 memory tiles (MTs), each one of which holds a four-way, 64 KB bank. Each MT also includes an on-chip network (OCN) router and a single-entry MSHR. Each bank may be configured as an L2 cache bank or as a scratchpad memory, by sending a configuration command across the OCN to a given MT. By aligning the OCN with the DTs, each IT/DT pair has its own private port into the secondary memory system, supporting high bandwidth into the cores for streaming applications. Details of the OCN beyond the description below can be found in [10].

The OCN consists of 16 MTs, each containing an OCN router and a level-2 cache bank. Twenty-four network tiles (NT), each containing an OCN router and the system address translation tables, surround the  $2 \times 8$  array of MTs. These together form a  $4 \times 10$ , 2D mesh, as shown in the left half of Figure 1.4. Connected to the OCN along the top and the bottom are the I/O tiles, including two DMA controllers, two SDRAM controllers (SDCs), the external bus controller (EBC), and the chip-to-chip network controller (C2C).

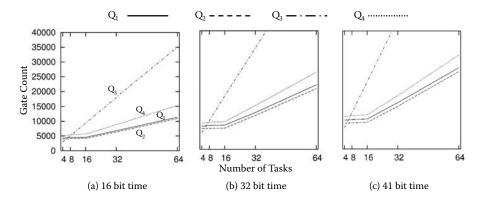

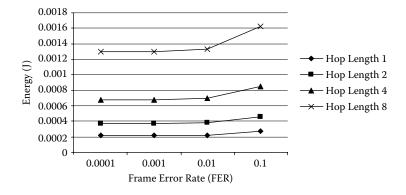

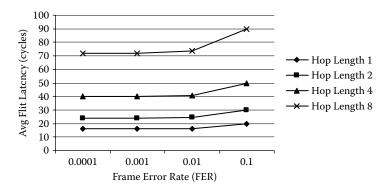

The OCN network is Y-X dimension-order, wormhole routed; flow control is credit-based, meaning that each node keeps track of the number of empty buffers in all of its neighbors' input FIFOs to determine when it is safe to send more data. Packets travel on one of four virtual channels, designated "Primary Request" (Q1), "Secondary Request" (Q2), "Secondary Reply" (P2), and "Primary Reply" (P1) in order of increasing priority. The packets range in size from 16 bytes to 80 bytes long, split into between one and five 16-byte flits.

OCN clients connect directly to NTs and include ten ports for instruction and data traffic to and from the two on-chip processors, two on-chip DMA controllers, two on-chip SDRAM controllers, one slow external bus controller, and one high-speed chip-to-chip controller. The C2C port is a direct extension of the OCN (albeit at one-eighth the bandwidth per channel), and enables TRIPS chips to be connected gluelessly to one another in a larger system. The OCN can be scaled by either increasing the mesh dimensions (more *M* and *N* tiles) or by utilizing the spare client connections on the east side.

#### 1.3.6.1 OCN Router

Figure 1.9 shows an MT along with its embedded OCN router. The OCN router is typical of virtual channel router designs. Incoming packets are

FIGURE 1.9 Memory tile block diagram highlighting OCN router in detail.

latched into one of the input FIFOs in one of five input directions, north, south, east, west, or local for the L2 bank itself. The router contains enough storage for two incoming flits of data per direction, per virtual channel. A  $4 \times 4$  crossbar network connects each input to every other possible output; a  $5 \times 5$  crossbar is unnecessary since a packet coming in from one direction cannot depart in that same direction. In cases of contention, the crossbar selects the higher priority channel. The router uses a round-robin arbitration scheme to resolve contention among requests at the same priority level. The direction of the last packet sent in each direction is stored and used on the next arbitration cycle to ensure routing fairness and livelock avoidance. A credit-based flow control scheme tracks the number of available buffers in neighboring receiver FIFOs. When a receiver removes a flit from an incoming FIFO, it sends a credit signal back to the sender to signify more FIFO buffer space is available for future flits.

#### 1.3.6.2 Network Address Translation

An NT forms a gateway to the OCN for clients, such as the TRIPS processors and IO units, to inject packets. Each NT contains an OCN router similar to that discussed in the previous section. The main difference is that the local interface is connected to an OCN client instead of an L2 cache bank. Virtual-to-system address translation is performed within processors using standard TLBs, but TRIPS supports an additional level of translation to enable reconfiguration of the memory system. An NT translates the system physical address to a network address using a simple table when the OCN client transmits a packet header to an NT. This table consists of 16 entries of eight bits each and is indexed using four bits from the system physical address. Each table entry contains the *X-Y* coordinates of the MT to which the address region is mapped. The table itself is memory mapped and can be modified on-the-fly by the runtime system. By adjusting the mapping functions within the TLBs and the network interface tiles (NTs), a programmer can configure the memory system in a variety of ways including as a single 1 MB shared level-2 cache, as two independent 512 KB level-2 caches (one per processor), as a 1 MB on-chip physical memory (no level-2 cache), or many combinations in between.

# 1.4 Distributed Microarchitectural Protocols

To enable concurrent, out-of-order execution on this distributed substrate, we implemented traditionally centralized microarchitectural functions, including fetch, execution, flush, and commit, with distributed protocols running across the control and data micronets.

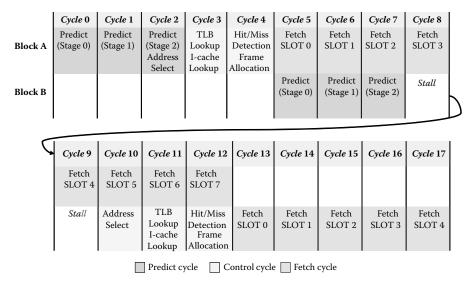

#### 1.4.1 Block Fetch Protocol

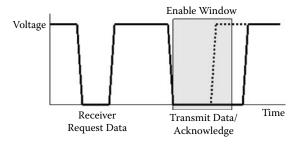

The fetch protocol retrieves a block of 128 TRIPS instructions from the ITs and distributes them into the array of ETs and RTs. Figure 1.10 shows the details of the GT's block fetch pipeline which takes a total of 13 cycles, including three cycles for prediction, 1 cycle for TLB and instruction cache tag access, and 1 cycle for hit/miss detection. On a cache hit, the GT sends eight pipelined indices out on the global dispatch network to the ITs. Prediction and instruction cache tag lookup for the next block is overlapped with the fetch commands of the current block. Running at peak, the machine can issue fetch commands every cycle with no bubbles, beginning a new block fetch every eight cycles.

When an IT receives a block dispatch command from the GT, it accesses its I-cache bank based on the index in the GDN message. In each of the next eight cycles the IT sends four instructions on its outgoing GDN paths to its associated row of ETs and RTs. These instructions are written into the read and write queues of the RTs and the reservation stations in the ETs when they arrive at their respective tiles, and are available to execute as soon as they arrive. Because the fetch commands and fetched instructions are delivered in a pipelined fashion across the ITs, ETs, and RTs, the furthest ET receives

**FIGURE 1.10** Fetch pipeline.

its first instruction packet 10 cycles and its last packet 17 cycles after the GT issues the first fetch command. Although the latency appears high, the pipelining enables a high-fetch bandwidth of 16 instructions per cycle in steady state, 1 instruction per ET per cycle.

On an I-cache miss, the GT instigates a distributed I-cache refill, using the global refill network to transmit the refill block's physical address to all of the ITs. Each IT processes the misses for its own chunk independently, and can simultaneously support one outstanding miss for each executing thread (up to four). When the two 64-byte cache lines for an IT's 128-byte block chunk return, and when the IT's south neighbor has finished its fill, the IT signals refill completion northward on the GSN. When the GT receives the refill completion signal from the top IT, it may issue a dispatch for that block to all ITs.

The distributed fetch protocol provides significantly higher fetch bandwidth compared to conventional processors. Directing the fetch from the GT obviates the need for reservation station management at every tile. Because a new set of reservation stations is required for executing every block, managing the free list of reservation stations in a distributed fashion and keeping them synchronized would require additional hardware mechanisms. Instead, by managing the free list in the GT and propagating the allocated identifier along with every fetch, the TRIPS implementation reduces the complexity in other tiles.

The implementation tightly couples the predictor operations and the fetch protocol operations in one single pipeline. In steady state, the three cycles for predict and three cycles for update can fully overlap with the eight cycles of fetch required for one block. Thus there are no bubbles in the fetch pipeline, enabling a new block fetch every eight cycles. This offers a peak fetch rate of 16 instructions per cycle (128 instruction/8 cycles) matching the peak execution rate of the processor. Occasionally, the predictor update operation may delay the predict operation causing bubbles in the fetch pipeline. For example, in Figure 1.10, an update operation starting in cycle 5 could delay the predict operation for the second block until cycle 8. The fetch of block B will not start until cycle 14, introducing a bubble in the pipeline.

An alternate design could have completely decoupled the prediction pipeline from the fetch pipeline using a fetch target buffer [22]. That design offers two advantages. First, multiple refills can be initiated well ahead of a fetch, offering prefetching benefits. Second, stalls in the predict pipeline are less likely to affect the fetch pipeline. Implementing this design would require additional block management in the fetch unit. Our analysis indicated that the extra complexity of the fetch target buffer was not worth the potential benefits in the current implementation.

#### 1.4.2 Distributed Execution

Dataflow execution of a block begins by the injection of block inputs from the RTs. An RT may begin to process an arriving read instruction even if the entire block has not yet been fetched. Each RT first searches the write queues of all older in-flight blocks. If no matching, in-flight write to that register is found, the RT simply reads that register from the architectural register file and forwards it to the consumers in the block via the OPN. If a matching write is found, the RT takes one of two actions: if the write instruction has received its value, the RT forwards that value to the read instruction's consumers. If the write instruction is still awaiting its value, the RT buffers the read instruction, which will be awakened by a tag broadcast when the pertinent write's value arrives.

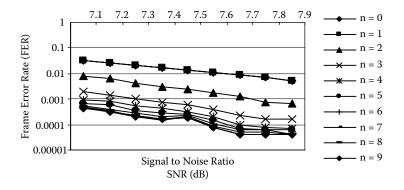

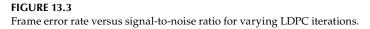

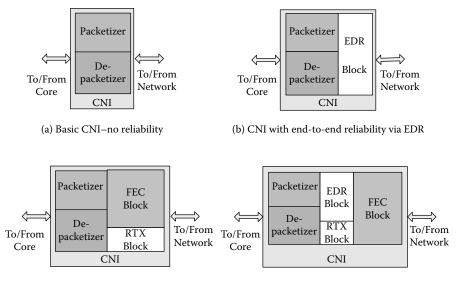

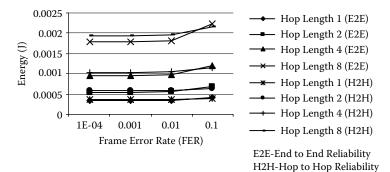

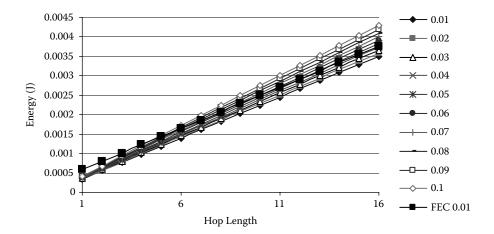

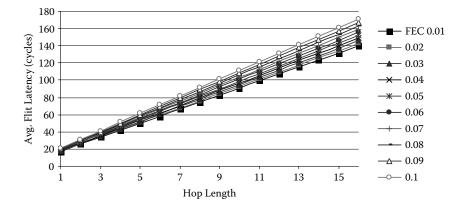

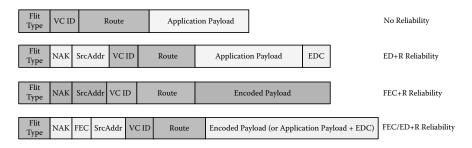

Arriving OPN operands wake up instructions within the ET, which selects and executes enabled instructions. The ET uses the target fields of the selected instruction to determine where to send the resulting operand. Arithmetic operands traverse the OPN to other ETs, whereas load and store instructions' addresses and data are sent on the OPN to the DTs. Branch instructions deliver their next block addresses to the GT via the OPN.