#### Contents

- 🛽 Main Page

- Table of content

- Copyright

- About the Author

- List of Figures

- List of Tables

- List of Examples

- Poreword [2]

- Preface

- Who Should Use This Book

- How This Book Is Organized

- Conventions Used in This Book

- Acknowledgments

- Part 1: Basic Verilog Topics

- Design with Verilog HDL

- 1.1 Evolution of Computer-Aided Digital Design

- 1.2 Emergence of HDLs

- 1.3 Typical Design Flow

- 1.4 Importance of HDLs

- 1.5 Popularity of Verilog HDL

- 1.6 Trends in HDLs

- Chapter 2. Hierarchical Modeling Concepts

- 2.1 Design Methodologies

- 2.2 4-bit Ripple Carry Counter

- 2.3 Modules

- 2.4 Instances

- 2.5 Components of a Simulation

- 2.6 Example

- 2.7 Summary

- 2.8 Exercises

- Chapter 3. Basic Concepts

- 3.1 Lexical Conventions

- 3.2 Data Types

- 3.3 System Tasks and Compiler Directives

- 3.4 Summary

- 3.5 Exercises

- Chapter 4. Modules and Ports

- 4.1 Modules

- 2 4.2 Ports

- 4.3 Hierarchical Names

- 4.4 Summary

- 4.5 Exercises

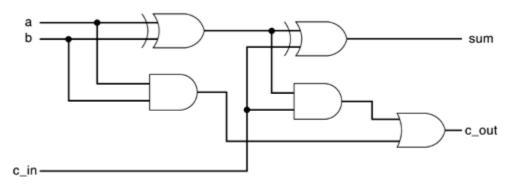

- Chapter 5. Gate-Level Modeling

- 5.1 Gate Types

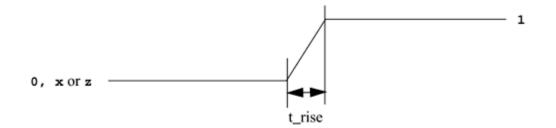

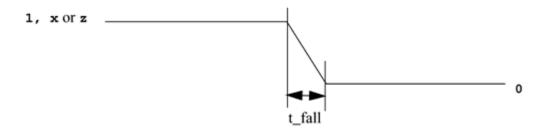

- 3.2 Gate Delays

- 3.3 Summary

- 5.4 Exercises

- Chapter 6. Dataflow Modeling

- 6.1 Continuous Assignments

- 6.2 Delays

- 6.3 Expressions, Operators, and Operands

- 6.4 Operator Types

- 3 6.5 Examples

- 3 6.6 Summary

- 3 6.7 Exercises

- Dhapter 7. Behavioral Modeling

- 7.1 Structured Procedures

- 7.2 Procedural Assignments

- 7.3 Timing Controls

- 7.4 Conditional Statements

- 7.5 Multiway Branching

- 7.6 Loops

- 7.7 Sequential and Parallel Blocks

- 7.8 Generate Blocks

- 7.9 Examples

- **?** 7.10 Summary

- 7.11 Exercises

- 1 Chapter 8. Tasks and Functions

- 8.1 Differences between Tasks and Functions

- 8.2 Tasks

- 8.3 Functions

- 8.4 Summary

- 8.5 Exercises

- Description of the second seco

- 9.1 Procedural Continuous Assignments

- 9.2 Overriding Parameters

- 2.3 Conditional Compilation and Execution

- 9.4 Time Scales

- 9.5 Useful System Tasks

- 2 9.6 Summary

- 9.7 Exercises

- Part 2: Advanced VerilogTopics

- Dhapter 10. Timing and Delays

- 10.1 Types of Delay Models

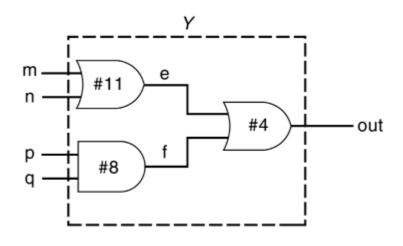

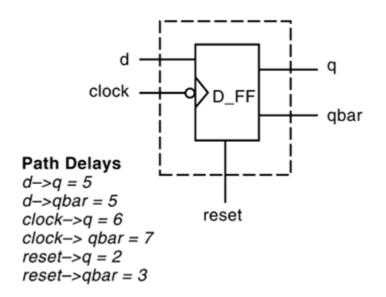

- 10.2 Path Delay Modeling

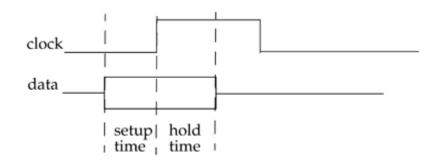

- 10.3 Timing Checks

- 10.4 Delay Back-Annotation

- 10.5 Summary

- 10.6 Exercises

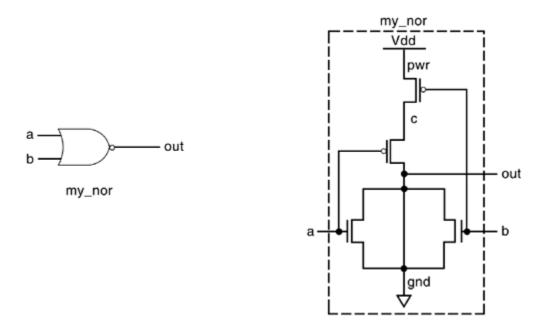

- Chapter 11. Switch-Level Modeling

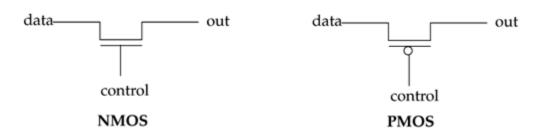

- 11.1 Switch-Modeling Elements

- 11.2 Examples

- 11.3 Summary

- 11.4 Exercises

- Dhapter 12. User-Defined Primitives

- 12.1 UDP basics

- 12.2 Combinational UDPs

- 12.3 Sequential UDPs

- 12.4 UDP Table Shorthand Symbols

- 12.5 Guidelines for UDP Design

- 12.6 Summary

- 12.7 Exercises

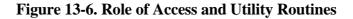

- Chapter 13. Programming Language Interface

- 13.1 Uses of PLI

- 13.2 Linking and Invocation of PLI Tasks

- 13.3 Internal Data Representation

- 13.4 PLI Library Routines

- **13.5** Summary

- 13.6 Exercises

- Chapter 14. Logic Synthesis with Verilog HDL

- 14.1 What Is Logic Synthesis?

- 14.2 Impact of Logic Synthesis

- 14.3 Verilog HDL Synthesis

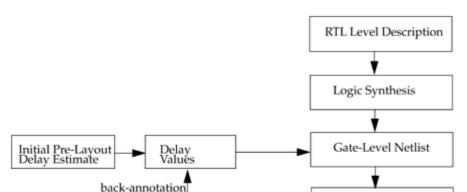

- 14.4 Synthesis Design Flow

- 14.5 Verification of Gate-Level Netlist

- 14.6 Modeling Tips for Logic Synthesis

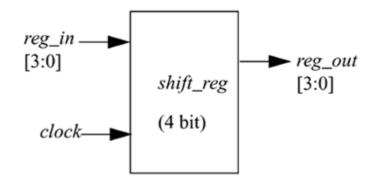

- 14.7 Example of Sequential Circuit Synthesis

- 14.9 Exercises

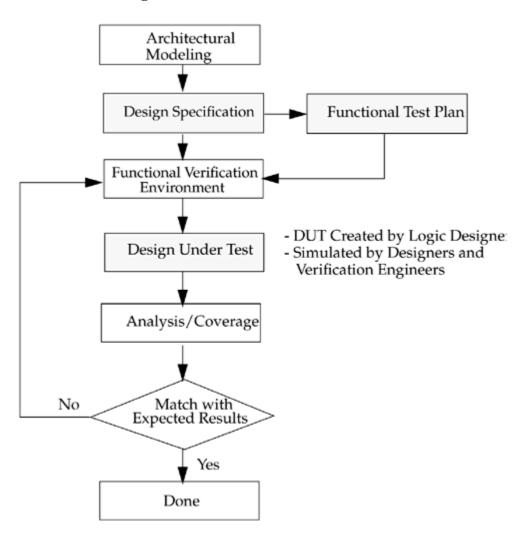

- Chapter 15. Advanced Verification Techniques

- 15.1 Traditional Verification Flow

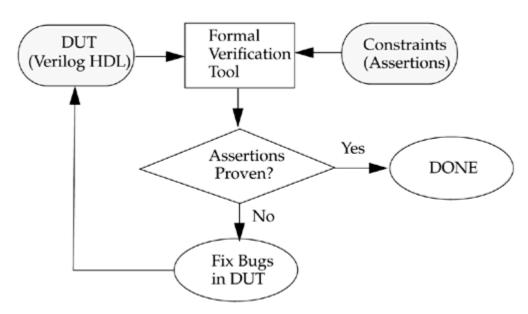

- 15.2 Assertion Checking

- 15.3 Formal Verification

- 15.4 Summary

- Part 3: Appendices

#### Manual Appendix A. Strength Modeling and Advanced Net Definitions

- A.1 Strength Levels

- A.2 Signal Contention

- A.3 Advanced Net Types

#### Dependix B. List of PLI Routines

- B.1 Conventions

- B.2 Access Routines

- B.3 Utility (tf\_) Routines

#### Appendix C. List of Keywords, System Tasks, and Compiler Directives

- C.1 Keywords

- C.2 System Tasks and Functions

- C.3 Compiler Directives

- Dependix D. Formal Syntax Definition

- D.1 Source Text

- D.2 Declarations

- D.3 Primitive Instances

- D.4 Module and Generated Instantiation

- D.5 UDP Declaration and Instantiation

- D.6 Behavioral Statements

- D.7 Specify Section

- D.8 Expressions

- D.9 General

- Endnotes

- Dependix E. Verilog Tidbits

- Origins of Verilog HDL

- Interpreted, Compiled, Native Compiled Simulators

- Event-Driven Simulation, Oblivious Simulation

- Cycle-Based Simulation

- Fault Simulation

- General Verilog Web sites

- Architectural Modeling Tools

- High-Level Verification Languages

- Simulation Tools

- Hardware Acceleration Tools

- In-Circuit Emulation Tools

- **Coverage Tools**

- Assertion Checking Tools

- Equivalence Checking Tools

- Pormal Verification Tools

- Dependix F. Verilog Examples

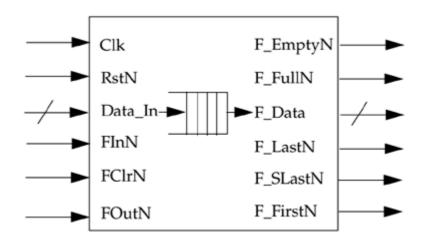

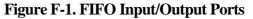

- P.1 Synthesizable FIFO Model

- F.2 Behavioral DRAM Model

#### Bibliography

- Manuals

- Books

- Quick Reference Guides

- About the CD-ROM

- Using the CD-ROM

- Technical Support

#### [Team LiB]

NEXT 🕨

Table of ContentsExamples

Verilog HDL: A Guide to Digital Design and Synthesis, Second Edition

By Samir Palnitkar

START READING Publisher: Prentice Hall PTR Pub Date: February 21, 2003 ISBN: 0-13-044911-3 Pages: 496

Written for both experienced and new users, this book gives you broad coverage of Verilog HDL. The book stresses the practical design and verification perspective of Verilog rather than emphasizing only the

language aspects. The information presented is fully compliant with the IEEE 1364-2001 Verilog HDL standard.

- •

- Describes state-of-the-art verification methodologies

- Provides full coverage of gate, dataflow (RTL), behavioral and switch modeling

- Introduces you to the Programming Language Interface (PLI)

- Describes logic synthesis methodologies

- Explains timing and delay simulation

- Discusses user-defined primitives

- Offers many practical modeling tips •

Includes over 300 illustrations, examples, and exercises, and a Verilog resource list.Learning objectives and summaries are provided for each chapter. NEXT 🕨 [Team LiB]

#### [Team LiB]

♦ PREVIOUS NEXT ►

Table of Contents Examples Verilog HDL: A Guide to Digital Design and Synthesis, Second Edition By Samir Palnitkar

START READING

Publisher: Prentice Hall PTR Pub Date: February 21, 2003 ISBN: 0-13-044911-3 Pages: 496

> Copyright About the Author List of Figures List of Tables List of Examples Foreword Preface Who Should Use This Book How This Book Is Organized Conventions Used in This Book Acknowledgments Part 1. Basic Verilog Topics Chapter 1. Overview of Digital Design with Verilog HDL Section 1.1. Evolution of Computer-Aided Digital Design Section 1.2. Emergence of HDLs Section 1.3. Typical Design Flow Section 1.4. Importance of HDLs Section 1.5. Popularity of Verilog HDL Section 1.6. Trends in HDLs Chapter 2. Hierarchical Modeling Concepts Section 2.1. Design Methodologies Section 2.2. 4-bit Ripple Carry Counter Section 2.3. Modules Section 2.4. Instances Section 2.5. Components of a Simulation Section 2.6. Example Section 2.7. Summary Section 2.8. Exercises Chapter 3. Basic Concepts Section 3.1. Lexical Conventions Section 3.2. Data Types Section 3.3. System Tasks and Compiler Directives Section 3.4. Summary Section 3.5. Exercises Chapter 4. Modules and Ports Section 4.1. Modules Section 4.2. Ports Section 4.3. Hierarchical Names Section 4.4. Summary Section 4.5. Exercises Chapter 5. Gate-Level Modeling Section 5.1. Gate Types Section 5.2. Gate Delays

Section 5.3. Summary Section 5.4. Exercises Chapter 6. Dataflow Modeling Section 6.1. Continuous Assignments Section 6.2. Delays Section 6.3. Expressions, Operators, and Operands Section 6.4. Operator Types Section 6.5. Examples Section 6.6. Summary Section 6.7. Exercises Chapter 7. Behavioral Modeling Section 7.1. Structured Procedures Section 7.2. Procedural Assignments Section 7.3. Timing Controls Section 7.4. Conditional Statements Section 7.5. Multiway Branching Section 7.6. Loops Section 7.7. Sequential and Parallel Blocks Section 7.8. Generate Blocks Section 7.9. Examples Section 7.10. Summary Section 7.11. Exercises Chapter 8. Tasks and Functions Section 8.1. Differences between Tasks and Functions Section 8.2. Tasks Section 8.3. Functions Section 8.4. Summary Section 8.5. Exercises Chapter 9. Useful Modeling Techniques Section 9.1. Procedural Continuous Assignments Section 9.2. Overriding Parameters Section 9.3. Conditional Compilation and Execution Section 9.4. Time Scales Section 9.5. Useful System Tasks Section 9.6. Summary Section 9.7. Exercises Part 2. Advanced VerilogTopics Chapter 10. Timing and Delays Section 10.1. Types of Delay Models Section 10.2. Path Delay Modeling Section 10.3. Timing Checks Section 10.4. Delay Back-Annotation Section 10.5. Summary Section 10.6. Exercises Chapter 11. Switch-Level Modeling Section 11.1. Switch-Modeling Elements Section 11.2. Examples Section 11.3. Summary Section 11.4. Exercises Chapter 12. User-Defined Primitives

Section 12.1. UDP basics Section 12.2. Combinational UDPs Section 12.3. Sequential UDPs Section 12.4. UDP Table Shorthand Symbols Section 12.5. Guidelines for UDP Design Section 12.6. Summary Section 12.7. Exercises Chapter 13. Programming Language Interface Section 13.1. Uses of PLI Section 13.2. Linking and Invocation of PLI Tasks Section 13.3. Internal Data Representation Section 13.4. PLI Library Routines Section 13.5. Summary Section 13.6. Exercises Chapter 14. Logic Synthesis with Verilog HDL Section 14.1. What Is Logic Synthesis? Section 14.2. Impact of Logic Synthesis Section 14.3. Verilog HDL Synthesis Section 14.4. Synthesis Design Flow Section 14.5. Verification of Gate-Level Netlist Section 14.6. Modeling Tips for Logic Synthesis Section 14.7. Example of Sequential Circuit Synthesis Section 14.9. Exercises Chapter 15. Advanced Verification Techniques Section 15.1. Traditional Verification Flow Section 15.2. Assertion Checking Section 15.3. Formal Verification Section 15.4. Summary Part 3. Appendices Appendix A. Strength Modeling and Advanced Net Definitions Section A.1. Strength Levels Section A.2. Signal Contention Section A.3. Advanced Net Types Appendix B. List of PLI Routines Section B.1. Conventions Section B.2. Access Routines Section B.3. Utility (tf\_) Routines Appendix C. List of Keywords, System Tasks, and Compiler Directives Section C.1. Keywords Section C.2. System Tasks and Functions Section C.3. Compiler Directives Appendix D. Formal Syntax Definition Section D.1. Source Text Section D.2. Declarations Section D.3. Primitive Instances Section D.4. Module and Generated Instantiation Section D.5. UDP Declaration and Instantiation Section D.6. Behavioral Statements Section D.7. Specify Section Section D.8. Expressions

Section D.9. General Endnotes Appendix E. Verilog Tidbits Origins of Verilog HDL Interpreted, Compiled, Native Compiled Simulators **Event-Driven Simulation**, Oblivious Simulation **Cycle-Based Simulation Fault Simulation** General Verilog Web sites Architectural Modeling Tools **High-Level Verification Languages Simulation Tools** Hardware Acceleration Tools **In-Circuit Emulation Tools Coverage Tools** Assertion Checking Tools **Equivalence Checking Tools** Formal Verification Tools Appendix F. Verilog Examples Section F.1. Synthesizable FIFO Model Section F.2. Behavioral DRAM Model **Bibliography** Manuals **Books** Quick Reference Guides About the CD-ROM Using the CD-ROM **Technical Support** ▲ PREVIOUS NEXT ▶ [Team LiB]

[Team LiB]

# Copyright

2003 Sun Microsystems, Inc. 2550 Garcia Avenue, Mountain View, California 94043-1100 U.S.A.

All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Portions of this product may be derived from the UNIX system and from the Berkeley 4.3 BSD system, licensed from the University of California. Third-party software, including font technology in this product, is protected by copyright and licensed from Sun's Suppliers.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 and FAR 52.227-19.

The product described in this manual may be protected by one or more U.S. patents, foreign patents, or pending applications.

#### TRADEMARKS

Sun, Sun Microsystems, the Sun logo, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and may be protected as trademarks in other countries. UNIX is a registered trademark in the United States and other countries, exclusively licensed through X/Open Company, Ltd. OPEN LOOK is a registered trademark of Novell, Inc. PostScript and Display PostScript are trademarks of Adobe Systems, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc. Verilog-XL is a trademark of Cadence Design Systems, Inc. VCS is a trademark of Viewlogic Systems, Inc. Magellan is a registered trademark of Systems Science, Inc. VirSim is a trademark of Simulation Technologies, Inc. Signalscan is a trademark of Design Acceleration, Inc. All other product, service, or company names mentioned herein are claimed as trademarks and trade names by their respective companies.

All SPARC trademarks, including the SCD Compliant Logo, are trademarks or registered trademarks of SPARC International, Inc. in the United States and may be protected as trademarks in other countries. SPARCcenter, SPARCcluster, SPARCompiler, SPARCdesign, SPARC811, SPARCengine, SPARCprinter, SPARCserver, SPARCstation, SPARCstorage, SPARCworks, microSPARC, microSPARC-II, and UltraSPARC are licensed exclusively to Sun Microsystems, Inc. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun Graphical User Interfaces were developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ▶

# **About the Author**

Samir Palnitkar is currently the President of Jambo Systems, Inc., a leading ASIC design and verification services company which specializes in high-end designs for microprocessor, networking, and communications applications. Mr. Palnitkar is a serial entrepreneur. He was the founder of Integrated Intellectual Property, Inc., an ASIC company that was acquired by Lattice Semiconductor, Inc. Later he founded Obongo, Inc., an e-commerce software firm that was acquired by AOL Time Warner, Inc.

Mr. Palnitkar holds a Bachelor of Technology in Electrical Engineering from Indian Institute of Technology, Kanpur, a Master's in Electrical Engineering from University of Washington, Seattle, and an MBA degree from San Jose State University, San Jose, CA.

Mr. Palnitkar is a recognized authority on Verilog HDL, modeling, verification, logic synthesis, and EDA-based methodologies in digital design. He has worked extensively with design and verification on various successful microprocessor, ASIC, and system projects. He was the lead developer of the Verilog framework for the shared memory, cache coherent, multiprocessor architecture, popularly known as the UltraSPARCTM Port Architecture, defined for Sun's next generation UltraSPARC-based desktop systems. Besides the UltraSPARC CPU, he has worked on a number of diverse design and verification projects at leading companies including Cisco, Philips, Mitsubishi, Motorola, National, Advanced Micro Devices, and Standard Microsystems.

Mr. Palnitkar was also a leading member of the group that first experimented with cycle-based simulation technology on joint projects with simulator companies. He has extensive experience with a variety of EDA tools such as Verilog-NC, Synopsys VCS, Specman, Vera, System Verilog, Synopsys, SystemC, Verplex, and Design Data Management Systems.

Mr. Palnitkar is the author of three US patents, one for a novel method to analyze finite state machines, a second for work on cycle-based simulation technology and a third(pending approval) for a unique e-commerce tool. He has also published several technical papers. In his spare time, Mr. Palnitkar likes to play cricket, read books, and travel the world.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# **List of Figures**

Figure 1-1 Typical Design Flow

Figure 2-1 Top-down Design Methodology

Figure 2-2 Bottom-up Design Methodology

Figure 2-3 Ripple Carry Counter

Figure 2-4 T-flipflop

Figure 2-5 Design Hierarchy

Figure 2-6 Stimulus Block Instantiates Design Block

Figure 2-7 Stimulus and Design Blocks Instantiated in a Dummy Top-Level Module

Figure 2-8 Stimulus and Output Waveforms

Figure 3-1 Example of Nets

Figure 4-1 Components of a Verilog Module

Figure 4-2 SR Latch

Figure 4-3 I/O Ports for Top and Full Adder

Figure 4-4 Port Connection Rules

Figure 4-5 Design Hierarchy for SR Latch Simulation

Figure 5-1 Basic Gates

#### [Team LiB]

[Team LiB]

A PREVIOUS NEXT ▶

## **List of Tables**

Table 3-1 Value Levels

Table 3-2 Strength Levels

Table 3-3 Special Characters

Table 3-4 String Format Specifications

Table 5-1 Truth Tables for And/Or Gates

Table 5-2 Truth Tables for Buf/Not Gates

Table 5-3 Truth Tables for Bufif/Notif Gates

Table 6-1 Operator Types and Symbols

Table 6-2 Equality Operators

Table 6-3 Truth Tables for Bitwise Operators

Table 6-4 Operator Precedence

Table 8-1

Tasks and Functions

Table 11-1 Logic Tables for NMOS and PMOS

Table 11-2 Strength Reduction by Resistive Switches

Table 11-3 Delay Specification on MOS and CMOS Switches

Table 11-4 Delay Specification for Bidirectional Switches

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# **List of Examples**

Example 2-1 Module Instantiation

Example 2-2 Illegal Module Nesting

Example 2-3 Ripple Carry Counter Top Block

Example 2-4 Flipflop T\_FF

Example 2-5 Flipflop D\_F

Example 2-6 Stimulus Block

Example 2-7 Output of the Simulation

Example 3-1 Example of Register

Example 3-2 Signed Register Declaration

Example 3-3 \$display Task

Example 3-4 Special Characters

Example 3-5 Monitor Statement

Example 3-6 Stop and Finish Tasks

Example 3-7 `define Directive

Example 3-8 `include Directive

Example 4-1 Components of SR Latch

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# Foreword

From a modest beginning in early 1984 at Gateway Design Automation, the Verilog hardware description language has become an industry standard as a result of extensive use in the design of integrated circuit chips and digital systems. Verilog came into being as a proprietary language supported by a simulation environment that was the first to support mixed-level design representations comprising switches, gates, RTL, and higher levels of abstractions of digital circuits. The simulation environment provided a powerful and uniform method to express digital designs as well as tests that were meant to verify such designs.

There were three key factors that drove the acceptance and dominance of Verilog in the marketplace. First, the introduction of the Programming Language Interface (PLI) permitted users of Verilog to literally extend and customize the simulation environment. Since then, users have exploited the PLI and their success at adapting Verilog to their environment has been a real winner for Verilog. The second key factor which drove Verilog's dominance came from Gateways paying close attention to the needs of the ASIC foundries and enhancing Verilog in close partnership with Motorola, National, and UTMC in the 1987-1989 time-frame. The realization that the vast majority of logic simulation was being done by designers of ASIC chips drove this effort. With ASIC foundries blessing the use of Verilog and even adopting it as their internal sign-off simulator, the industry acceptance of Verilog was driven even further. The third and final key factor behind the success of Verilog was the introduction of Verilog-based synthesis technology by Synopsys in 1987. Gateway licensed its proprietary Verilog language to Synopsys for this purpose. The combination of the simulation and synthesis technologies served to make Verilog the language of choice for the hardware designers.

The arrival of the VHDL (VHSIC Hardware Description Language), along with the powerful alignment of the remaining EDA vendors driving VHDL as an IEEE standard, led to the placement of Verilog in the public domain. Verilog was inducted as the IEEE 1364 standard in 1995. Since 1995, many enhancements were made to Verilog HDL based on requests from Verilog users. These changes were incorporated into the latest IEEE 1364-2001 Verilog standard. Today, Verilog has become the language of choice for digital design and is the basis for synthesis, verification, and place and route technologies.

Samir's book is an excellent guide to the user of the Verilog language. Not only does it explain the language constructs with a rich variety of examples, it also goes into details of the usage of the PLI and the application of synthesis technology. The topics in the book are arranged logically and flow very smoothly. This book is written from a very practical design perspective rather than with a focus simply on the syntax aspects of the language.

This second edition of Samir's book is unique in two ways. Firstly, it incorporates all enhancements described in IEEE 1364-2001 standard. This ensures that the readers of the book are working with the latest information on Verilog. Secondly, a new chapter has been added on advanced verification techniques that are now an integral part of Verilog-based methodologies. Knowledge of these techniques is critical to Verilog users who design and verify multi-million gate systems.

I can still remember the challenges of teaching Verilog and its associated design and verification methodologies to users. By using Samir's book, beginning users of Verilog will become productive sooner, and experienced Verilog users will get the latest in a convenient reference book that can refresh their understanding of Verilog. This book is a must for any Verilog user.

#### Prabhu Goel

Former President of Gateway Design Automation

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ▶

# Preface

During my earliest experience with Verilog HDL, I was looking for a book that could give me a "jump start" on using Verilog HDL. I wanted to learn basic digital design paradigms and the necessary Verilog HDL constructs that would help me build small digital circuits, using Verilog and run simulations. After I had gained some experience with building basic Verilog models, I wanted to learn to use Verilog HDL to build larger designs. At that time, I was searching for a book that broadly discussed advanced Verilog-based digital design concepts and real digital design methodologies. Finally, when I had gained enough experience with digital design and verification of real IC chips, though manuals of Verilog-based products were available, from time to time, I felt the need for a Verilog HDL book that would act as a handy reference. A desire to fill this need led to the publication of the first edition of this book.

It has been more than six years since the publication of the first edition. Many changes have occurred during these years. These years have added to the depth and richness of my design and verification experience through the diverse variety of ASIC and microprocessor projects that I have successfully completed in this duration. I have also seen state-of-the-art verification methodologies and tools evolve to a high level of maturity. The IEEE 1364-2001 standard for Verilog HDL has been approved. The purpose of this second edition is to incorporate the IEEE 1364-2001 additions and introduce to Verilog users the latest advances in verification. I hope to make this edition a richer learning experience for the reader.

This book emphasizes breadth rather than depth. The book imparts to the reader a working knowledge of a broad variety of Verilog-based topics, thus giving the reader a global understanding of Verilog HDL-based design. The book leaves the in-depth coverage of each topic to the Verilog HDL language reference manual and the reference manuals of the individual Verilog-based products.

This book should be classified not only as a Verilog HDL book but, more generally, as a digital design book. It is important to realize that Verilog HDL is only a tool used in digital design. It is the means to an end?he digital IC chip. Therefore, this book stresses the practical design perspective more than the mere language aspects of Verilog HDL. With HDL-based digital design having become a necessity, no digital designer can afford to ignore HDLs.

[Team LiB]

▲ PREVIOUS NEXT ►

[Team LiB]

◀ PREVIOUS NEXT ►

## Who Should Use This Book

The book is intended primarily for beginners and intermediate-level Verilog users. However, for advanced Verilog users, the broad coverage of topics makes it an excellent reference book to be used in conjunction with the manuals and training materials of Verilog-based products.

The book presents a logical progression of Verilog HDL-based topics. It starts with the basics, such as HDL-based design methodologies, and then gradually builds on the basics to eventually reach advanced topics, such as PLI or logic synthesis. Thus, the book is useful to Verilog users with varying levels of expertise as explained below.

- •

- Students in logic design courses at universities

- <u>Part 1</u> of this book is ideal for a foundation semester course in Verilog HDL-based logic design. Students are exposed to hierarchical modeling concepts, basic Verilog constructs and modeling techniques, and the necessary knowledge to write small models and run simulations.

- •

- New Verilog users in the industry

- Companies are moving to Verilog HDL- based design. <u>Part 1</u> of this book is a perfect jump start for designers who want to orient their skills toward HDL-based design.

- •

- Users with basic Verilog knowledge who need to understand advanced concepts

- <u>Part 2</u> of this book discusses advanced concepts, such as UDPs, timing simulation, PLI, and logic synthesis, which are necessary for graduation from small Verilog models to larger designs.

- •

- Verilog experts

- All Verilog topics are covered, from the basics modeling constructs to advanced topics like PLIs, logic synthesis, and advanced verification techniques. For Verilog experts, this book is a handy reference to be used along with the IEEE Standard Verilog Hardware Description Language reference manual.

The material in the book sometimes leans toward an Application Specific Integrated Circuit (ASIC) design methodology. However, the concepts explained in the book are general enough to be applicable to the design of FPGAs, PALs, buses, boards, and systems. The book uses Medium Scale Integration (MSI) logic examples to simplify discussion. The same concepts apply to VLSI designs.

[Team LiB]

[Team LiB]

♦ PREVIOUS NEXT ►

## How This Book Is Organized

This book is organized into three parts.

Part 1, Basic Verilog Topics, covers all information that a new user needs to build small Verilog models and run simulations. Note that in Part 1, gate-level modeling is addressed before behavioral modeling. I have chosen to do so because I think that it is easier for a new user to see a 1-1 correspondence between gate-level circuits and equivalent Verilog descriptions. Once gate-level modeling is understood, a new user can move to higher levels of abstraction, such as data flow modeling and behavioral modeling, without losing sight of the fact that Verilog HDL is a language for digital design and is not a programming language. Thus, a new user starts off with the idea that Verilog is a language for digital design. New users who start with behavioral modeling often tend to write Verilog the way they write their C programs. They sometimes lose sight of the fact that they are trying to represent hardware circuits by using Verilog. Part 1 contains nine chapters.

Part 2, Advanced Verilog Topics, contains the advanced concepts a Verilog user needs to know to graduate from small Verilog models to larger designs. Advanced topics such as timing simulation, switch-level modeling, UDPs, PLI, logic synthesis, and advanced verification techniques are covered. Part 2 contains six chapters.

Part 3, Appendices, contains information useful as a reference. Useful information, such as strength-level modeling, list of PLI routines, formal syntax definition, Verilog tidbits, and large Verilog examples is included. Part 3 contains six appendices.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

## **Conventions Used in This Book**

Table PR-1 describes the type changes and symbols used in this book.

Table PR-1. Typographic Conventions

| Typeface or Symbol | Description                                                                         | Examples                             |

|--------------------|-------------------------------------------------------------------------------------|--------------------------------------|

| AaBbCc123          | Keywords, system tasks and<br>compiler directives that are a<br>part of Verilog HDL | and, nand, \$display, `define        |

| AaBbCc123          | Emphasis                                                                            | cell characterization, instantiation |

| AaBbCc123          | Names of signals, modules, ports, etc.                                              | fulladd4, D_FF, out                  |

A few other conventions need to be clarified.

- •

- In the book, use of Verilog and Verilog HDL refers to the "Verilog Hardware Description Language." Any reference to a Verilog-based simulator is specifically mentioned, using words such as Verilog simulator or trademarks such as Verilog-XL or VCS.

- •

- The word designer is used frequently in the book to emphasize the digital design perspective. However, it is a general term used to refer to a Verilog HDL user or a verification engineer.

[Team LiB]

PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ►

# Acknowledgments

The first edition of this book was written with the help of a great many people who contributed their energies to this project. Following were the primary contributors to my creation: John Sanguinetti, Stuart Sutherland, Clifford Cummings, Robert Emberley, Ashutosh Mauskar, Jack McKeown, Dr. Arun Somani, Dr. Michael Ciletti, Larry Ke, Sunil Sabat, Cheng-I Huang, Maqsoodul Mannan, Ashok Mehta, Dick Herlein, Rita Glover, Ming-Hwa Wang, Subramanian Ganesan, Sandeep Aggarwal, Albert Lau, Samir Sanghani, Kiran Buch, Anshuman Saha, Bill Fuchs, Babu Chilukuri, Ramana Kalapatapu, Karin Ellison and Rachel Borden. I would like to start by thanking all those people once again.

For this second edition, I give special thanks to the following people who helped me with the review process and provided valuable feedback:

Anders Nordstrom

Stefen Boyd

Clifford Cummings

Harry Foster

Yatin Trivedi

Rajeev Madhavan

John Sanguinetti

Dr. Arun Somani

Michael McNamara

Berend Ozceri

Shrenik Mehta

Mike Meredith

ASIC Consultant

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# **Part 1: Basic Verilog Topics**

#### 1 Overview of Digital Design with Verilog HDL

Evolution of CAD, emergence of HDLs, typical HDL-based design flow, why Verilog HDL?, trends in HDLs.

#### 2 Hierarchical Modeling Concepts

Top-down and bottom-up design methodology, differences between modules and module instances, parts of a simulation, design block, stimulus block.

#### **3 Basic Concepts**

Lexical conventions, data types, system tasks, compiler directives.

#### 4 Modules and Ports

Module definition, port declaration, connecting ports, hierarchical name referencing.

#### 5 Gate-Level Modeling

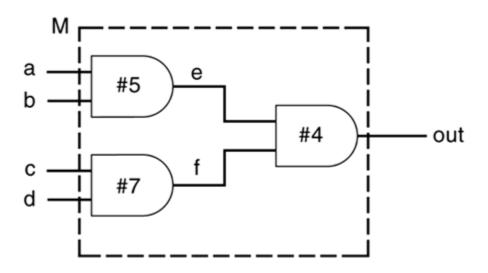

Modeling using basic Verilog gate primitives, description of and/or and buf/not type gates, rise, fall and turn-off delays, min, max, and typical delays.

#### 6 Dataflow Modeling

Continuous assignments, delay specification, expressions, operators, operands, operator types.

#### 7 Behavioral Modeling

Structured procedures, initial and always, blocking and nonblocking statements, delay control, generate statement, event control, conditional statements, multiway branching, loops, sequential and parallel blocks.

#### 8 Tasks and Functions

Differences between tasks and functions, declaration, invocation, automatic tasks and functions.

#### 9 Useful Modeling Techniques

Procedural continuous assignments, overriding parameters, conditional compilation and execution, useful system tasks [Team LiB]

PREVIOUS NEXT ►

[Team LiB]

A PREVIOUS NEXT ►

# Chapter 1. Overview of Digital Design with Verilog HDL

- Section 1.1. Evolution of Computer-Aided Digital Design

- <u>Section 1.2. Emergence of HDLs</u>

- Section 1.3. Typical Design Flow

- Section 1.4. Importance of HDLs

- Section 1.5. Popularity of Verilog HDL

- Section 1.6. Trends in HDLs

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

## **1.1 Evolution of Computer-Aided Digital Design**

Digital circuit design has evolved rapidly over the last 25 years. The earliest digital circuits were designed with vacuum tubes and transistors. Integrated circuits were then invented where logic gates were placed on a single chip. The first integrated circuit (IC) chips were SSI (Small Scale Integration) chips where the gate count was very small. As technologies became sophisticated, designers were able to place circuits with hundreds of gates on a chip. These chips were called MSI (Medium Scale Integration) chips. With the advent of LSI (Large Scale Integration), designers could put thousands of gates on a single chip. At this point, design processes started getting very complicated, and designers felt the need to automate these processes. Electronic Design Automation (EDA)[1] techniques began to evolve. Chip designers began to use circuit and logic simulation techniques to verify the functionality of building blocks of the order of about 100 transistors. The circuits were still tested on the breadboard, and the layout was done on paper or by hand on a graphic computer terminal.

[1] The earlier edition of the book used the term CAD tools. Technically, the term Computer-Aided Design (CAD) tools refers to back-end tools that perform functions related to place and route, and layout of the chip . The term Computer-Aided Engineering (CAE) tools refers to tools that are used for front-end processes such HDL simulation, logic synthesis, and timing analysis. Designers used the terms CAD and CAE interchangeably. Today, the term Electronic Design Automation is used for both CAD and CAE. For the sake of simplicity, in this book, we will refer to all design tools as EDA tools.

With the advent of VLSI (Very Large Scale Integration) technology, designers could design single chips with more than 100,000 transistors. Because of the complexity of these circuits, it was not possible to verify these circuits on a breadboard. Computer-aided techniques became critical for verification and design of VLSI digital circuits. Computer programs to do automatic placement and routing of circuit layouts also became popular. The designers were now building gate-level digital circuits manually on graphic terminals. They would build small building blocks and then derive higher-level blocks from them. This process would continue until they had built the top-level block. Logic simulators came into existence to verify the functionality of these circuits before they were fabricated on chip.

As designs got larger and more complex, logic simulation assumed an important role in the design process. Designers could iron out functional bugs in the architecture before the chip was designed further.

[Team LiB]

▲ PREVIOUS NEXT ▶

[Team LiB]

## **1.2 Emergence of HDLs**

For a long time, programming languages such as FORTRAN, Pascal, and C were being used to describe computer programs that were sequential in nature. Similarly, in the digital design field, designers felt the need for a standard language to describe digital circuits. Thus, Hardware Description Languages (HDLs) came into existence. HDLs allowed the designers to model the concurrency of processes found in hardware elements. Hardware description languages such as Verilog HDL and VHDL became popular. Verilog HDL originated in 1983 at Gateway Design Automation. Later, VHDL was developed under contract from DARPA. Both Verilog and VHDL simulators to simulate large digital circuits quickly gained acceptance from designers.

Even though HDLs were popular for logic verification, designers had to manually translate the HDL-based design into a schematic circuit with interconnections between gates. The advent of logic synthesis in the late 1980s changed the design methodology radically. Digital circuits could be described at a register transfer level (RTL) by use of an HDL. Thus, the designer had to specify how the data flows between registers and how the design processes the data. The details of gates and their interconnections to implement the circuit were automatically extracted by logic synthesis tools from the RTL description.

Thus, logic synthesis pushed the HDLs into the forefront of digital design. Designers no longer had to manually place gates to build digital circuits. They could describe complex circuits at an abstract level in terms of functionality and data flow by designing those circuits in HDLs. Logic synthesis tools would implement the specified functionality in terms of gates and gate interconnections.

HDLs also began to be used for system-level design. HDLs were used for simulation of system boards, interconnect buses, FPGAs (Field Programmable Gate Arrays), and PALs (Programmable Array Logic). A common approach is to design each IC chip, using an HDL, and then verify system functionality via simulation.

Today, Verilog HDL is an accepted IEEE standard. In 1995, the original standard IEEE 1364-1995 was approved. IEEE 1364-2001 is the latest Verilog HDL standard that made significant improvements to the original standard.

[Team LiB]

■ PREVIOUS NEXT ▶

[Team LiB]

♦ PREVIOUS NEXT ►

## **1.3 Typical Design Flow**

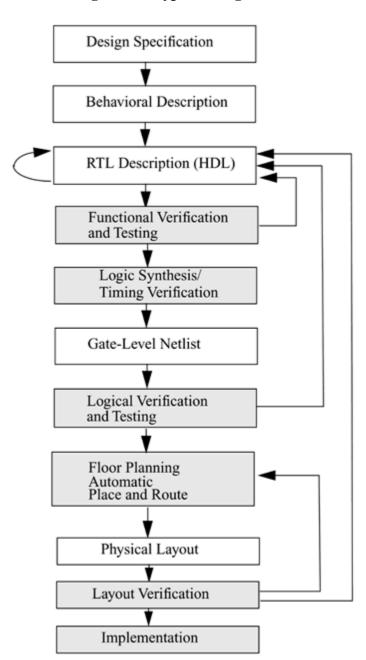

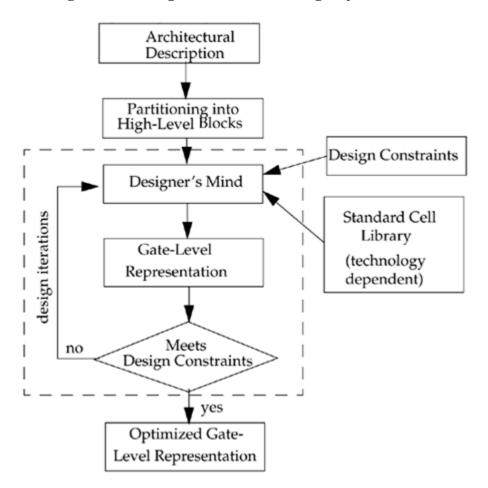

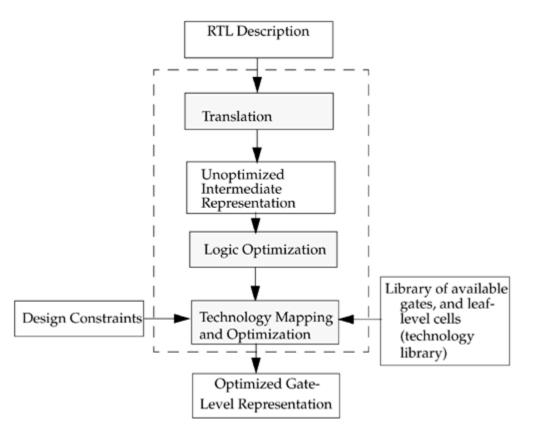

A typical design flow for designing VLSI IC circuits is shown in <u>Figure 1-1</u>. Unshaded blocks show the level of design representation; shaded blocks show processes in the design flow.

Figure 1-1. Typical Design Flow

The design flow shown in Figure 1-1 is typically used by designers who use HDLs. In any design, specifications are written first. Specifications describe abstractly the functionality, interface, and overall architecture of the digital circuit to be designed. At this point, the architects do not need to think about how they will implement this circuit. A behavioral description is then created to analyze the design in terms of functionality, performance, compliance to standards, and other high-level issues. Behavioral descriptions are often written with HDLs.[2]

[2] New EDA tools have emerged to simulate behavioral descriptions of circuits. These tools combine the powerful concepts from HDLs and object oriented languages such as C++. These tools can be used instead of writing behavioral descriptions in Verilog HDL.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

A PREVIOUS NEXT ►

## **1.4 Importance of HDLs**

HDLs have many advantages compared to traditional schematic-based design.

- •

- Designs can be described at a very abstract level by use of HDLs. Designers can write their RTL description without choosing a specific fabrication technology. Logic synthesis tools can automatically convert the design to any fabrication technology. If a new technology emerges, designers do not need to redesign their circuit. They simply input the RTL description to the logic synthesis tool and create a new gate-level netlist, using the new fabrication technology. The logic synthesis tool will optimize the circuit in area and timing for the new technology.

- •

- By describing designs in HDLs, functional verification of the design can be done early in the design cycle. Since designers work at the RTL level, they can optimize and modify the RTL description until it meets the desired functionality. Most design bugs are eliminated at this point. This cuts down design cycle time significantly because the probability of hitting a functional bug at a later time in the gate-level netlist or physical layout is minimized.

- •

- Designing with HDLs is analogous to computer programming. A textual description with comments is an easier way to develop and debug circuits. This also provides a concise representation of the design, compared to gate-level schematics. Gate-level schematics are almost incomprehensible for very complex designs.

HDL-based design is here to stay. [3] With rapidly increasing complexities of digital circuits and increasingly sophisticated EDA tools, HDLs are now the dominant method for large digital designs. No digital circuit designer can afford to ignore HDL-based design.

[3] New tools and languages focused on verification have emerged in the past few years. These languages are better suited for functional verification. However, for logic design, HDLs continue as the preferred choice.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ►

## **1.5 Popularity of Verilog HDL**

Verilog HDL has evolved as a standard hardware description language. Verilog HDL offers many useful features

- •

- Verilog HDL is a general-purpose hardware description language that is easy to learn and easy to use. It is similar in syntax to the C programming language. Designers with C programming experience will find it easy to learn Verilog HDL.

- •

- Verilog HDL allows different levels of abstraction to be mixed in the same model. Thus, a designer can define a hardware model in terms of switches, gates, RTL, or behavioral code. Also, a designer needs to learn only one language for stimulus and hierarchical design.

- •

- Most popular logic synthesis tools support Verilog HDL. This makes it the language of choice for designers.

- •

- All fabrication vendors provide Verilog HDL libraries for postlogic synthesis simulation. Thus, designing a chip in Verilog HDL allows the widest choice of vendors.

- •

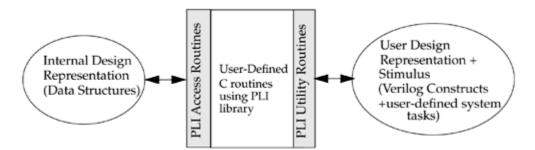

- The Programming Language Interface (PLI) is a powerful feature that allows the user to write custom C code to interact with the internal data structures of Verilog. Designers can customize a Verilog HDL simulator to their needs with the PLI.

#### [ Team LiB ]

#### PREVIOUS NEXT NEX NEXT NEX NEXT NEX

[Team LiB]

## **1.6 Trends in HDLs**

The speed and complexity of digital circuits have increased rapidly. Designers have responded by designing at higher levels of abstraction. Designers have to think only in terms of functionality. EDA tools take care of the implementation details. With designer assistance, EDA tools have become sophisticated enough to achieve a close-to-optimum implementation.

The most popular trend currently is to design in HDL at an RTL level, because logic synthesis tools can create gate-level netlists from RTL level design. Behavioral synthesis allowed engineers to design directly in terms of algorithms and the behavior of the circuit, and then use EDA tools to do the translation and optimization in each phase of the design. However, behavioral synthesis did not gain widespread acceptance. Today, RTL design continues to be very popular. Verilog HDL is also being constantly enhanced to meet the needs of new verification methodologies.

Formal verification and assertion checking techniques have emerged. Formal verification applies formal mathematical techniques to verify the correctness of Verilog HDL descriptions and to establish equivalency between RTL and gate-level netlists. However, the need to describe a design in Verilog HDL will not go away. Assertion checkers allow checking to be embedded in the RTL code. This is a convenient way to do checking in the most important parts of a design.

New verification languages have also gained rapid acceptance. These languages combine the parallelism and hardware constructs from HDLs with the object oriented nature of C++. These languages also provide support for automatic stimulus creation, checking, and coverage. However, these languages do not replace Verilog HDL. They simply boost the productivity of the verification process. Verilog HDL is still needed to describe the design.

For very high-speed and timing-critical circuits like microprocessors, the gate-level netlist provided by logic synthesis tools is not optimal. In such cases, designers often mix gate-level description directly into the RTL description to achieve optimum results. This practice is opposite to the high-level design paradigm, yet it is frequently used for high-speed designs because designers need to squeeze the last bit of timing out of circuits, and EDA tools sometimes prove to be insufficient to achieve the desired results.

Another technique that is used for system-level design is a mixed bottom-up methodology where the designers use either existing Verilog HDL modules, basic building blocks, or vendor-supplied core blocks to quickly bring up their system simulation. This is done to reduce development costs and compress design schedules. For example, consider a system that has a CPU, graphics chip, I/O chip, and a system bus. The CPU designers would build the next-generation CPU themselves at an RTL level, but they would use behavioral models for the graphics chip and the I/O chip and would buy a vendor-supplied model for the system bus. Thus, the system-level simulation for the CPU could be up and running very quickly and long before the RTL descriptions for the graphics chip and the I/O chip are completed.

[Team LiB]

#### ♦ PREVIOUS NEXT ►

#### [Team LiB]

#### A PREVIOUS NEXT ▶

# **Chapter 2. Hierarchical Modeling Concepts**

Before we discuss the details of the Verilog language, we must first understand basic hierarchical modeling concepts in digital design. The designer must use a "good" design methodology to do efficient Verilog HDL-based design. In this chapter, we discuss typical design methodologies and illustrate how these concepts are translated to Verilog. A digital simulation is made up of various components. We talk about the components and their interconnections.

Learning Objectives

- •

- Understand top-down and bottom-up design methodologies for digital design.

- •

- Explain differences between modules and module instances in Verilog.

- •

- Describe four levels of abstraction?ehavioral, data flow, gate level, and switch level?o represent the same module.

- •

- Describe components required for the simulation of a digital design. Define a stimulus block and a design block. Explain two methods of applying stimulus.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ►

### 2.1 Design Methodologies

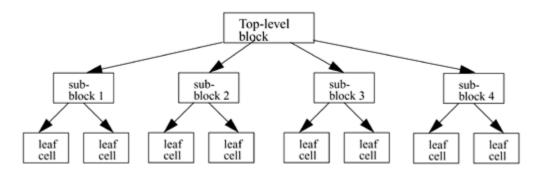

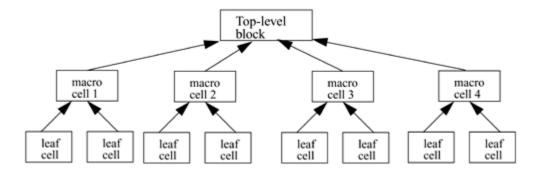

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology. In a top-down design methodology, we define the top-level block and identify the sub-blocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided. Figure 2-1 shows the top-down design process.

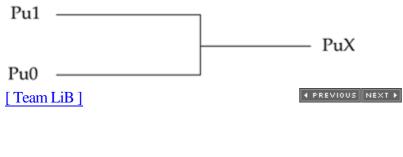

Figure 2-1. Top-down Design Methodology

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design. Figure 2-2 shows the bottom-up design process.

Figure 2-2. Bottom-up Design Methodology

Typically, a combination of top-down and bottom-up flows is used. Design architects define the specifications of the top-level block. Logic designers decide how the design should be structured by breaking up the functionality into blocks and sub-blocks. At the same time, circuit designers are designing optimized circuits for leaf-level cells. They build higher-level cells by using these leaf cells. The flow meets at an intermediate point where the switch-level circuit designers have created a library of leaf cells by using switches, and the logic level designers have designed from top-down until all modules are defined in terms of leaf cells.

To illustrate these hierarchical modeling concepts, let us consider the design of a negative edge-triggered 4-bit ripple carry counter described in Section 2.2, 4-bit Ripple Carry Counter.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

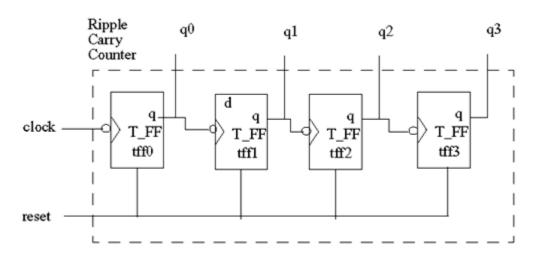

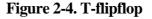

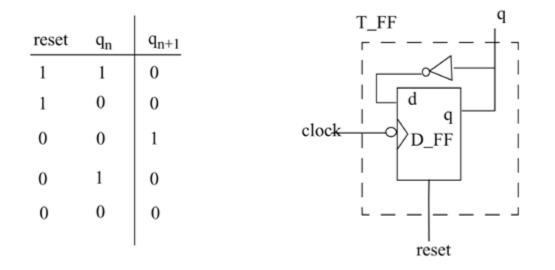

# 2.2 4-bit Ripple Carry Counter

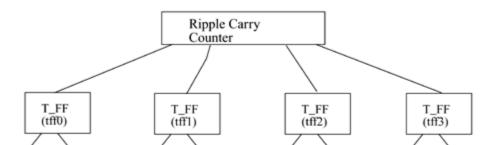

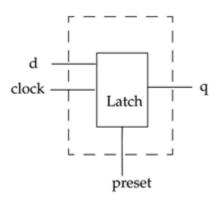

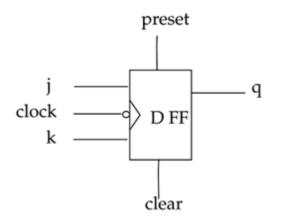

The ripple carry counter shown in Figure 2-3 is made up of negative edge-triggered toggle flipflops (T\_FF). Each of the T\_FFs can be made up from negative edge-triggered D-flipflops (D\_FF) and inverters (assuming q\_bar output is not available on the D\_FF), as shown in Figure 2-4.

**Figure 2-3. Ripple Carry Counter**

Thus, the ripple carry counter is built in a hierarchical fashion by using building blocks. The diagram for the design hierarchy is shown in Figure 2-5.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# 2.3 Modules

We now relate these hierarchical modeling concepts to Verilog. Verilog provides the concept of a module. A module is the basic building block in Verilog. A module can be an element or a collection of lower-level design blocks. Typically, elements are grouped into modules to provide common functionality that is used at many places in the design. A module provides the necessary functionality to the higher-level block through its port interface (inputs and outputs), but hides the internal implementation. This allows the designer to modify module internals without affecting the rest of the design.

In Figure 2-5, ripple carry counter, T\_FF, D\_FF are examples of modules. In Verilog, a module is declared by the keyword module. A corresponding keyword endmodule must appear at the end of the module definition. Each module must have a module\_name, which is the identifier for the module, and a module\_terminal\_list, which describes the input and output terminals of the module.

```

module <module_name> (<module_terminal_list>);

...

<module internals>

...

endmodule

```

Specifically, the T-flipflop could be defined as a module as follows:

```

module T_FF (q, clock, reset);

.

.

.

.

.

.

.

endmodule

```

Verilog is both a behavioral and a structural language. Internals of each module can be defined at four levels of abstraction, depending on the needs of the design. The module behaves identically with the external environment irrespective of the level of abstraction at which the module is described. The internals of the module are hidden from the environment. Thus, the level of abstraction to describe a module can be changed without any change in the environment. These levels will be studied in detail in separate chapters later in the book. The levels are defined below.

- Behavioral or algorithmic level

- This is the highest level of abstraction provided by Verilog HDL. A module can be implemented in terms of the desired design algorithm without concern for the hardware implementation details. Designing at this level is very similar to C programming.

- ٠

- Dataflow level

- At this level, the module is designed by specifying the data flow. The designer is aware of how

<sup>•</sup>

# [Team LiB]

[Team LiB]

■ PREVIOUS NEXT

■

# **2.4 Instances**

A module provides a template from which you can create actual objects. When a module is invoked, Verilog creates a unique object from the template. Each object has its own name, variables, parameters, and I/O interface. The process of creating objects from a module template is called instantiation, and the objects are called instances. In Example 2-1, the top-level block creates four instances from the T-flipflop (T\_FF) template. Each T\_FF instantiates a D\_FF and an inverter gate. Each instance must be given a unique name. Note that // is used to denote single-line comments.

### **Example 2-1 Module Instantiation**

```

// Define the top-level module called ripple carry

// counter. It instantiates 4 T-flipflops. Interconnections are

// shown in Section 2.2, 4-bit Ripple Carry Counter.

module ripple_carry_counter(q, clk, reset);

output [3:0] q; //I/O signals and vector declarations

//will be explained later.

input clk, reset; //I/O signals will be explained later.

//Four instances of the module T_FF are created. Each has a unique

//name.Each instance is passed a set of signals. Notice, that

//each instance is a copy of the module T FF.

T_FF tff0(q[0],clk, reset);

T_FF tff1(q[1],q[0], reset);

T_FF tff2(q[2],q[1], reset);

T_FF tff3(q[3],q[2], reset);

endmodule

// Define the module T_FF. It instantiates a D-flipflop. We assumed

// that module D-flipflop is defined elsewhere in the design. Refer

// to Figure 2-4 for interconnections.

module T_FF(q, clk, reset);

//Declarations to be explained later

output q;

input clk, reset;

wire d;

D_FF dff0(q, d, clk, reset); // Instantiate D_FF. Call it dff0.

not n1(d, q); // not gate is a Verilog primitive. Explained later.

```

endmodule

In Verilog, it is illegal to nest modules. One module definition cannot contain another module definition within the module and endmodule statements. Instead, a module definition can incorporate copies of other modules by instantiating them. It is important not to confuse module definitions and instances of a module. Module definitions simply specify how the module will work, its internals, and its interface. Modules must be instantiated for use in the design.

Example 2-2 shows an illegal module nesting where the module T\_FF is defined inside the module definition of the ripple carry counter.

## **Example 2-2 Illegal Module Nesting**

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# 2.5 Components of a Simulation

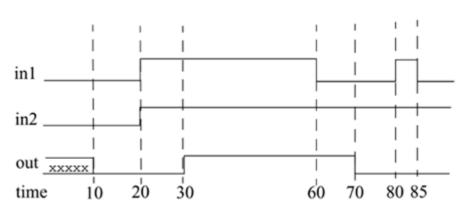

Once a design block is completed, it must be tested. The functionality of the design block can be tested by applying stimulus and checking results. We call such a block the stimulus block. It is good practice to keep the stimulus and design blocks separate. The stimulus block can be written in Verilog. A separate language is not required to describe stimulus. The stimulus block is also commonly called a test bench. Different test benches can be used to thoroughly test the design block.

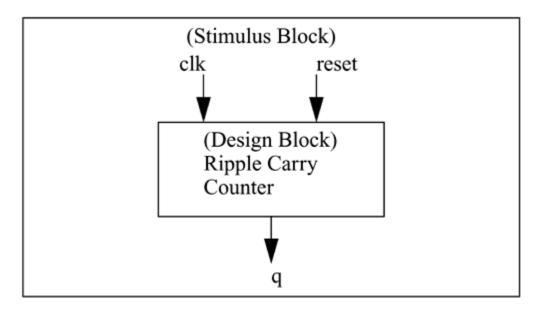

Two styles of stimulus application are possible. In the first style, the stimulus block instantiates the design block and directly drives the signals in the design block. In <u>Figure 2-6</u>, the stimulus block becomes the top-level block. It manipulates signals clk and reset, and it checks and displays output signal q.

Figure 2-6. Stimulus Block Instantiates Design Block

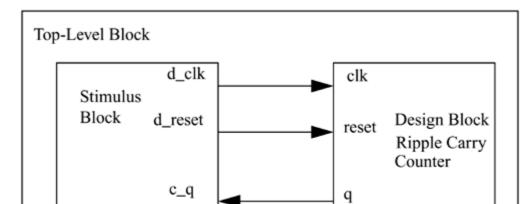

The second style of applying stimulus is to instantiate both the stimulus and design blocks in a top-level dummy module. The stimulus block interacts with the design block only through the interface. This style of applying stimulus is shown in Figure 2-7. The stimulus module drives the signals d\_clk and d\_reset, which are connected to the signals clk and reset in the design block. It also checks and displays signal c\_q, which is connected to the signal q in the design block. The function of top-level block is simply to instantiate the design and stimulus blocks.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# 2.6 Example

To illustrate the concepts discussed in the previous sections, let us build the complete simulation of a ripple carry counter. We will define the design block and the stimulus block. We will apply stimulus to the design block and monitor the outputs. As we develop the Verilog models, you do not need to understand the exact syntax of each construct at this stage. At this point, you should simply try to understand the design process. We discuss the syntax in much greater detail in the later chapters.

## 2.6.1 Design Block

We use a top-down design methodology. First, we write the Verilog description of the top-level design block (Example 2-3), which is the ripple carry counter (see Section 2.2, 4-bit Ripple Carry Counter).

#### **Example 2-3 Ripple Carry Counter Top Block**

```

module ripple_carry_counter(q, clk, reset);

output [3:0] q;

input clk, reset;

//4 instances of the module T_FF are created.

T_FF tff0(q[0],clk, reset);

T_FF tff1(q[1],q[0], reset);

T_FF tff2(q[2],q[1], reset);

T_FF tff3(q[3],q[2], reset);

endmodule

```

In the above module, four instances of the module T\_FF (T-flipflop) are used. Therefore, we must now define (Example 2-4) the internals of the module T\_FF, which was shown in Figure 2-4.

#### Example 2-4 Flipflop T\_FF

```

module T_FF(q, clk, reset);

output q;

input clk, reset;

wire d;

D_FF dff0(q, d, clk, reset);

not n1(d, q); // not is a Verilog-provided primitive. case sensitive

endmodule

```

Since T\_FF instantiates D\_FF, we must now define (Example 2-5) the internals of module D\_FF. We assume asynchronous reset for the D\_FFF.

### Example 2-5 Flipflop D\_F

// module D\_FF with synchronous reset

module D\_FF(q, d, clk, reset);

output q;

```

input d, clk, reset;

reg q;

```

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

▲ PREVIOUS NEXT ►

# 2.7 Summary

In this chapter we discussed the following concepts.

- •

- Two kinds of design methodologies are used for digital design: top-down and bottom-up. A combination of these two methodologies is used in today's digital designs. As designs become very complex, it is important to follow these structured approaches to manage the design process.

- •

- Modules are the basic building blocks in Verilog. Modules are used in a design by instantiation. An instance of a module has a unique identity and is different from other instances of the same module. Each instance has an independent copy of the internals of the module. It is important to understand the difference between modules and instances.

- •

- There are two distinct components in a simulation: a design block and a stimulus block. A stimulus block is used to test the design block. The stimulus block is usually the top-level block. There are two different styles of applying stimulus to a design block.

- •

- The example of the ripple carry counter explains the step-by-step process of building all the blocks required in a simulation.

This chapter is intended to give an understanding of the design process and how Verilog fits into the design process. The details of Verilog syntax are not important at this stage and will be dealt with in later chapters.

[Team LiB]

◀ PREVIOUS NEXT ►

[Team LiB]

♦ PREVIOUS NEXT ►

# 2.8 Exercises

## 1:

An interconnect switch (IS) contains the following components, a shared memory (MEM), a system controller (SC) and a data crossbar (Xbar).

### a.

- a. Define the modules MEM, SC, and Xbar, using the module/endmodule keywords. You do not need to define the internals. Assume that the modules have no terminal lists.

- b.

- b. Define the module IS, using the module/endmodule keywords. Instantiate the modules MEM, SC, Xbar and call the instances mem1, sc1, and xbar1, respectively. You do not need to define the internals. Assume that the module IS has no terminals.

- C.

- c. Define a stimulus block (Top), using the module/endmodule keywords. Instantiate the design block IS and call the instance is1. This is the final step in building the simulation environment.

## 2:

A 4-bit ripple carry adder (Ripple\_Add) contains four 1-bit full adders (FA).

## a.

- a. Define the module FA. Do not define the internals or the terminal list.

- b.

- b. Define the module Ripple\_Add. Do not define the internals or the terminal list.

Instantiate four full adders of the type FA in the module Ripple\_Add and call them fa0, fa1, fa2, and fa3.

#### ♦ PREVIOUS NEXT ►

[Team LiB]

[Team LiB]

♦ PREVIOUS NEXT ►

# **Chapter 3. Basic Concepts**

In this chapter, we discuss the basic constructs and conventions in Verilog. These conventions and constructs are used throughout the later chapters. These conventions provide the necessary framework for Verilog HDL. Data types in Verilog model actual data storage and switch elements in hardware very closely. This chapter may seem dry, but understanding these concepts is a necessary foundation for the successive chapters.

Learning Objectives

•

- Understand lexical conventions for operators, comments, whitespace, numbers, strings, and identifiers.

- •

- Define the logic value set and data types such as nets, registers, vectors, numbers, simulation time, arrays, parameters, memories, and strings.

- •

- Identify useful system tasks for displaying and monitoring information, and for stopping and finishing the simulation.

- •

- Learn basic compiler directives to define macros and include files.

[Team LiB]

◀ PREVIOUS NEXT ▶

[Team LiB]

#### A PREVIOUS NEXT ►

# **3.1 Lexical Conventions**

The basic lexical conventions used by Verilog HDL are similar to those in the C programming language. Verilog contains a stream of tokens. Tokens can be comments, delimiters, numbers, strings, identifiers, and keywords. Verilog HDL is a case-sensitive language. All keywords are in lowercase.

## 3.1.1 Whitespace

Blank spaces (b), tabs (t) and newlines (n) comprise the whitespace. Whitespace is ignored by Verilog except when it separates tokens. Whitespace is not ignored in strings.

# 3.1.2 Comments

Comments can be inserted in the code for readability and documentation. There are two ways to write comments. A one-line comment starts with "//". Verilog skips from that point to the end of line. A multiple-line comment starts with "/\*" and ends with "\*/". Multiple-line comments cannot be nested. However, one-line comments can be embedded in multiple-line comments.

a = b && c; // This is a one-line comment

/\* This is a multiple line

comment \*/

/\* This is /\* an illegal \*/ comment \*/

/\* This is //a legal comment \*/

# 3.1.3 Operators

Operators are of three types: unary, binary, and ternary. Unary operators precede the operand. Binary operators appear between two operands. Ternary operators have two separate operators that separate three operands.

a =  $\sim$  b; //  $\sim$  is a unary operator. b is the operand a = b && c; // && is a binary operator. b and c are operands a = b ? c : d; // ?: is a ternary operator. b, c and d are operands

# **3.1.4 Number Specification**

There are two types of number specification in Verilog: sized and unsized.

#### Sized numbers

Sized numbers are represented as <size> '<base format> <number>.

<size> is written only in decimal and specifies the number of bits in the number. Legal base formats are decimal ('d or 'D), hexadecimal ('h or 'H), binary ('b or 'B) and octal ('o or 'O). The number is specified

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# 3.2 Data Types

This section discusses the data types used in Verilog.

# 3.2.1 Value Set

Verilog supports four values and eight strengths to model the functionality of real hardware. The four value levels are listed in Table 3-1.

Table 3-1. Value Levels

| Value Level | Condition in Hardware Circuits |  |

|-------------|--------------------------------|--|

| 0           | Logic zero, false condition    |  |

| 1           | Logic one, true condition      |  |

| x           | Unknown logic value            |  |

| Z           | High impedance, floating state |  |

In addition to logic values, strength levels are often used to resolve conflicts between drivers of different strengths in digital circuits. Value levels 0 and 1 can have the strength levels listed in Table 3-2.

Table 3-2. Strength Levels

| Strength Level | Туре    | Degree    |

|----------------|---------|-----------|

| supply         | Driving | strongest |

| strong         | Driving |           |

| pull           | Driving |           |

| large          | Storage |           |

| weak           | Driving |           |

| medium         | Storage |           |

| small          | Storage |           |

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# **3.3 System Tasks and Compiler Directives**

In this section, we introduce two special concepts used in Verilog: system tasks and compiler directives.

# 3.3.1 System Tasks

Verilog provides standard system tasks for certain routine operations. All system tasks appear in the form \$<keyword>. Operations such as displaying on the screen, monitoring values of nets, stopping, and finishing are done by system tasks. We will discuss only the most useful system tasks. Other tasks are listed in Verilog manuals provided by your simulator vendor or in the IEEE Standard Verilog Hardware Description Language specification.

## **Displaying information**

\$display is the main system task for displaying values of variables or strings or expressions. This is one of the most useful tasks in Verilog.

Usage: \$display(p1, p2, p3,...., pn);

p1, p2, p3,..., pn can be quoted strings or variables or expressions. The format of \$display is very similar to printf in C. A \$display inserts a newline at the end of the string by default. A \$display without any arguments produces a newline.

Strings can be formatted using the specifications listed in <u>Table 3-4</u>. For more detailed specifications, see IEEE Standard Verilog Hardware Description Language specification.

Table 3-4. String Format Specifications

| Format   | Display                                          |

|----------|--------------------------------------------------|

| %d or %D | Display variable in decimal                      |

| %b or %B | Display variable in binary                       |

| %s or %S | Display string                                   |

| %h or %H | Display variable in hex                          |

| %c or %C | Display ASCII character                          |

| %m or %M | Display hierarchical name (no argument required) |

[Team LiB]

♦ PREVIOUS NEXT ▶

[Team LiB]

◀ PREVIOUS NEXT ►

# 3.4 Summary

We discussed the basic concepts of Verilog in this chapter. These concepts lay the foundation for the material discussed in the further chapters.

- •

- Verilog is similar in syntax to the C programming language . Hardware designers with previous C programming experience will find Verilog easy to learn.

- •

- Lexical conventions for operators, comments, whitespace, numbers, strings, and identifiers were discussed.

- •

- Various data types are available in Verilog. There are four logic values, each with different strength levels. Available data types include nets, registers, vectors, numbers, simulation time, arrays, memories, parameters, and strings. Data types represent actual hardware elements very closely.

- •

- Verilog provides useful system tasks to do functions like displaying, monitoring, suspending, and finishing a simulation.

- •

- Compiler directive `define is used to define text macros, and `include is used to include other Verilog files.

▲ PREVIOUS NEXT ▶

# [Team LiB]

[Team LiB]

# **3.5 Exercises**

1:

Practice writing the following numbers:

a.

- a. Decimal number 123 as a sized 8-bit number in binary. Use \_ for readability.

- b.

- b. A 16-bit hexadecimal unknown number with all x's.

- C.

- c. A 4-bit negative 2 in decimal . Write the 2's complement form for this number.

- d.

- d. An unsized hex number 1234.

## 2:

Are the following legal strings? If not, write the correct strings.

a.

a. "This is a string displaying the % sign"b.

b. "out = in1 + in2"

C.

c. "Please ring a bell 007"

d.

d. "This is a backslash  $\ \ n$ "

# 3:

Are these legal identifiers?

a.

- a. system1

- b.

b. 1reg

- C.

- c. \$latch d.

[Team LiB]

[Team LiB]

#### ▲ PREVIOUS NEXT ▶

♦ PREVIOUS NEXT ►

# **Chapter 4. Modules and Ports**

In the previous chapters, we acquired an understanding of the fundamental hierarchical modeling concepts, basic conventions, and Verilog constructs. In this chapter, we take a closer look at modules and ports from the Verilog language point of view.

Learning Objectives

•

- Identify the components of a Verilog module definition, such as module names, port lists, parameters, variable declarations, dataflow statements, behavioral statements, instantiation of other modules, and tasks or functions.

- •

- Understand how to define the port list for a module and declare it in Verilog.

- •

- Describe the port connection rules in a module instantiation.

- •

- Understand how to connect ports to external signals, by ordered list, and by name.

- •

- Explain hierarchical name referencing of Verilog identifiers.

[Team LiB]

♦ PREVIOUS NEXT

♦

[Team LiB]

♦ PREVIOUS NEXT ►

# 4.1 Modules

We discussed how a module is a basic building block in <u>Chapter 2</u>, Hierarchical Modeling Concepts. We ignored the internals of modules and concentrated on how modules are defined and instantiated. In this section, we analyze the internals of the module in greater detail.

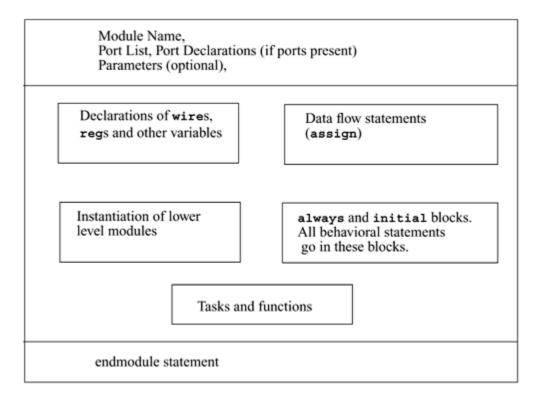

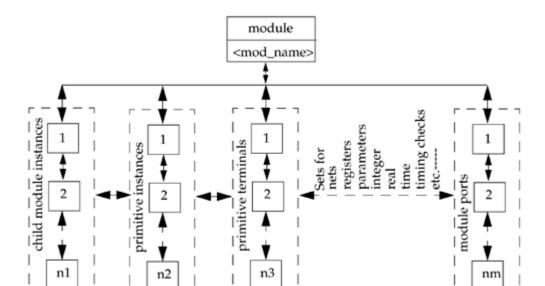

A module in Verilog consists of distinct parts, as shown in Figure 4-1.

Figure 4-1. Components of a Verilog Module

A module definition always begins with the keyword module. The module name, port list, port declarations, and optional parameters must come first in a module definition. Port list and port declarations are present only if the module has any ports to interact with the external environment. The five components within a module are: variable declarations, dataflow statements, instantiation of lower modules, behavioral blocks, and tasks or functions. These components can be in any order and at any place in the module definition. The endmodule statement must always come last in a module definition. All components except module, module name, and endmodule are optional and can be mixed and matched as per design needs. Verilog allows multiple modules to be defined in a single file. The modules can be defined in any order in the file.

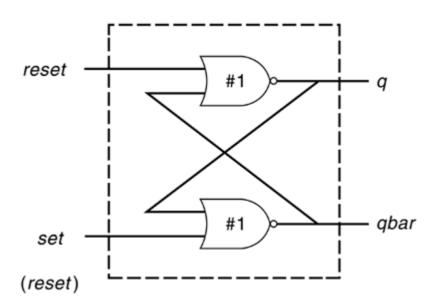

To understand the components of a module shown above, let us consider a simple example of an SR latch, as shown in Figure 4-2.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# 4.2 Ports

Ports provide the interface by which a module can communicate with its environment. For example, the input/output pins of an IC chip are its ports. The environment can interact with the module only through its ports. The internals of the module are not visible to the environment. This provides a very powerful flexibility to the designer. The internals of the module can be changed without affecting the environment as long as the interface is not modified. Ports are also referred to as terminals.

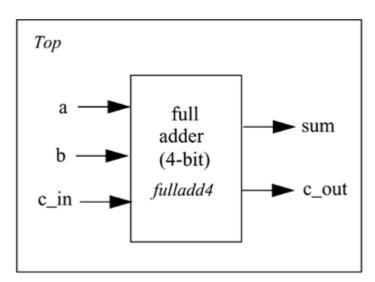

# 4.2.1 List of Ports

A module definition contains an optional list of ports. If the module does not exchange any signals with the environment, there are no ports in the list. Consider a 4-bit full adder that is instantiated inside a top-level module Top. The diagram for the input/output ports is shown in Figure 4-3.

Figure 4-3. I/O Ports for Top and Full Adder

Notice that in the above figure, the module Top is a top-level module. The module fulladd4 is instantiated below Top. The module fulladd4 takes input on ports a, b, and c\_in and produces an output on ports sum and c\_out. Thus, module fulladd4 performs an addition for its environment. The module Top is a top-level module in the simulation and does not need to pass signals to or receive signals from the environment. Thus, it does not have a list of ports. The module names and port lists for both module declarations in Verilog are as shown in Example 4-2.

## **Example 4-2 List of Ports**

module fulladd4(sum, c\_out, a, b, c\_in); //Module with a list of ports

module Top; // No list of ports, top-level module in simulation

# **4.2.2 Port Declaration**

All ports in the list of ports must be declared in the module. Ports can be declared as follows:

[Team LiB]

♦ PREVIOUS NEXT ►

[ Team LiB ]

# **4.3 Hierarchical Names**

We described earlier how Verilog supports a hierarchical design methodology. Every module instance, signal, or variable is defined with an identifier. A particular identifier has a unique place in the design hierarchy. Hierarchical name referencing allows us to denote every identifier in the design hierarchy with a unique name. A hierarchical name is a list of identifiers separated by dots (".") for each level of hierarchy. Thus, any identifier can be addressed from any place in the design by simply specifying the complete hierarchical name of that identifier.

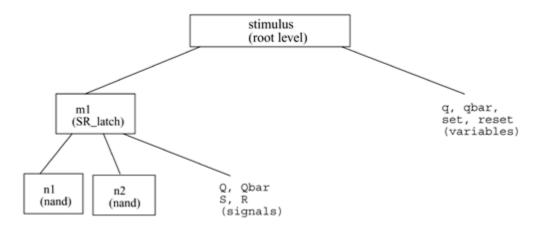

The top-level module is called the root module because it is not instantiated anywhere. It is the starting point. To assign a unique name to an identifier, start from the top-level module and trace the path along the design hierarchy to the desired identifier. To clarify this process, let us consider the simulation of SR latch in Example 4-1. The design hierarchy is shown in Figure 4-5.

#### Figure 4-5. Design Hierarchy for SR Latch Simulation

For this simulation, stimulus is the top-level module. Since the top-level module is not instantiated anywhere, it is called the root module. The identifiers defined in this module are q, qbar, set, and reset. The root module instantiates m1, which is a module of type SR\_latch. The module m1 instantiates nand gates n1 and n2. Q, Qbar, S, and R are port signals in instance m1. Hierarchical name referencing assigns a unique name to each identifier. To assign hierarchical names, use the module name for root module and instance names for all module instances below the root module. Example 4-8 shows hierarchical names for all identifiers in the above simulation. Notice that there is a dot (.) for each level of hierarchy from the root module to the desired identifier.

#### **Example 4-8 Hierarchical Names**

| stimulus       | stimulus.q       |  |

|----------------|------------------|--|

| stimulus.qbar  | stimulus.set     |  |

| stimulus.reset | stimulus.m1      |  |

| stimulus.ml.Q  | stimulus.ml.Qbar |  |

| stimulus.m1.S  | stimulus.ml.R    |  |

| stimulus.nl    | stimulus.n2      |  |

|                |                  |  |

Each identifier in the design is uniquely specified by its hierarchical path name. To display the level of hierarchy, use the special character %m in the \$display task. See <u>Table 3-4</u>, String Format Specifications, for details.

## [Team LiB]

[Team LiB]

♦ PREVIOUS NEXT ►

♦ PREVIOUS NEXT ►

# 4.4 Summary

In this chapter, we discussed the following aspects of Verilog:

- •

- Module definitions contain various components. Keywords module and endmodule are mandatory. Other components?ort list, port declarations, variable and signal declarations, dataflow statements, behavioral blocks, lower-level module instantiations, and tasks or functions?re optional and can be added as needed.

- •

- Ports provide the module with a means to communicate with other modules or its environment. A module can have a port list. Ports in the port list must be declared as input, output, or inout. When instantiating a module, port connection rules are enforced by the Verilog simulator. An ANSI C style embeds the port declarations in the module definition statement.

- •

- Ports can be connected by name or by ordered list.

- •

- Each identifier in the design has a unique hierarchical name. Hierarchical names allow us to address any identifier in the design from any other level of hierarchy in the design.

[Team LiB]

♦ PREVIOUS NEXT ►

[Team LiB]

# **4.5 Exercises**

#### 1: